#### **COMPUTER ARCHITECTURE**

Chapter 3 – CPU Pipelining

Prof. Dr.-Ing. Stefan Wallentowitz

Department 07 – Munich University of Applied Sciences

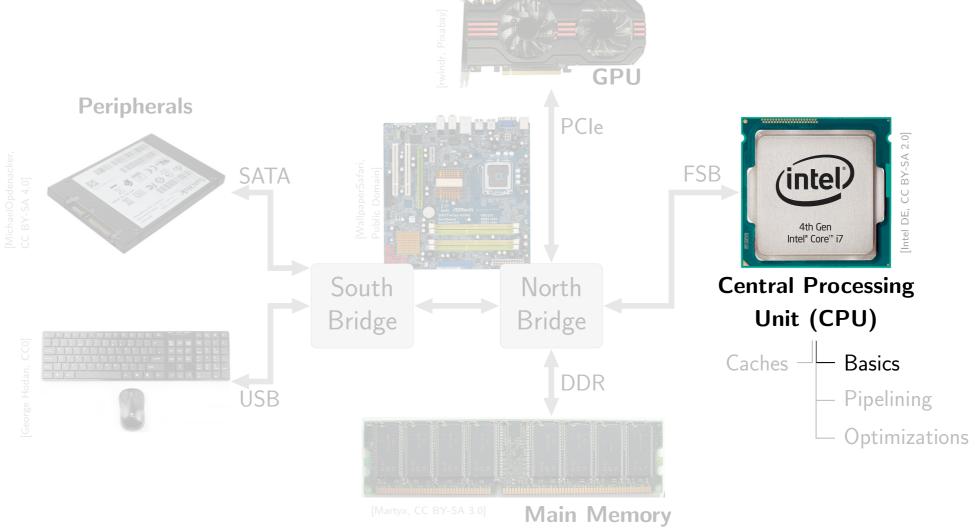

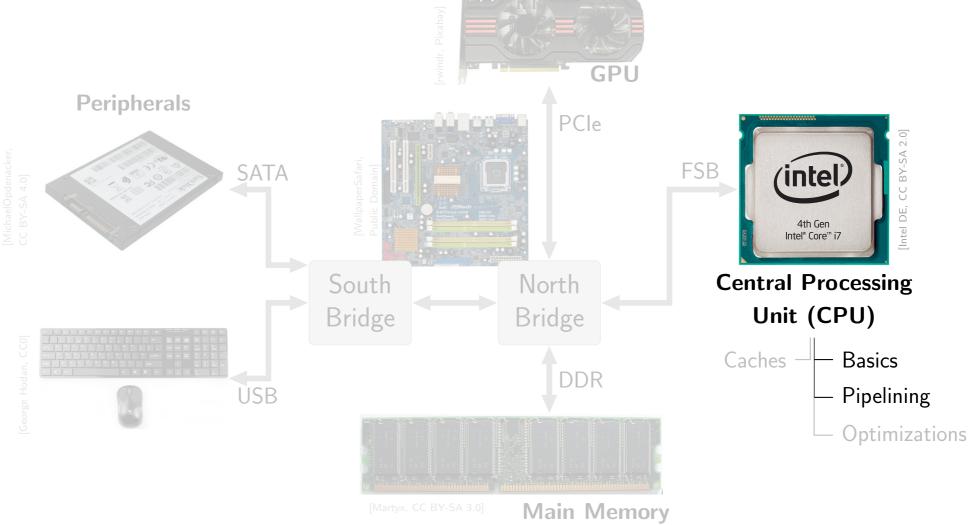

# **Course Organization**

Computer Architecture - Chapter 3 - CPU Pipelining

# **Course Organization**

Computer Architecture - Chapter 3 - CPU Pipelining

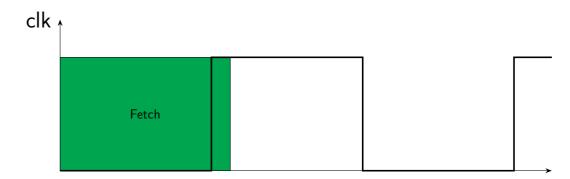

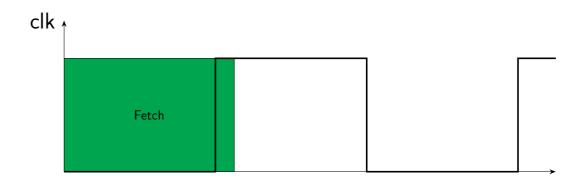

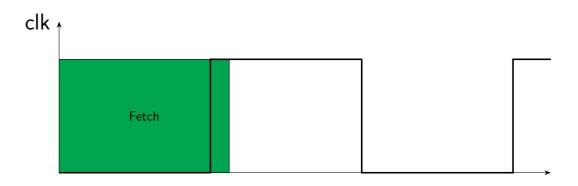

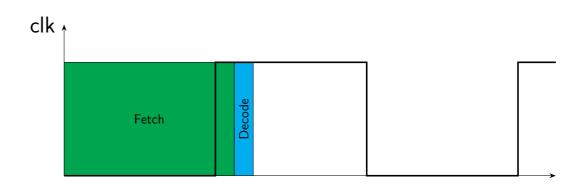

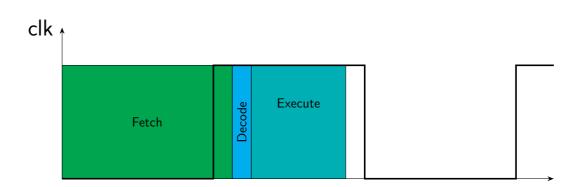

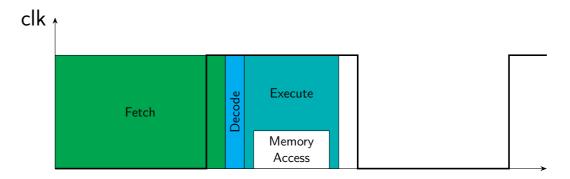

**Fetch instruction** (short: FE)

#### **Fetch instruction** (short: FE)

Pointer to next instruction from current program counter

#### **Fetch instruction** (short: FE)

- Pointer to next instruction from current program counter

- Load the instruction from memory

### **Fetch instruction** (short: FE)

- Pointer to next instruction from current program counter

- Load the instruction from memory

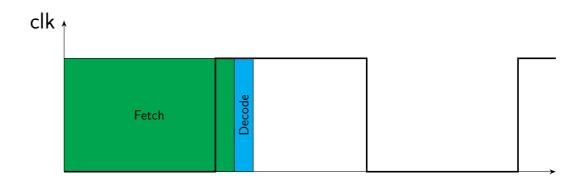

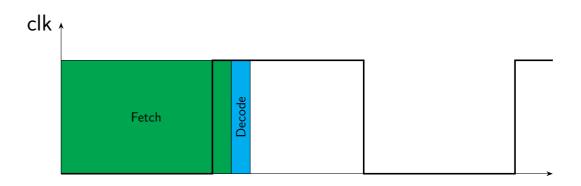

#### **Decode instruction (DE)**

#### Fetch instruction (short: FE)

- Pointer to next instruction from current program counter

- Load the instruction from memory

#### **Decode instruction (DE)**

Get operands from register file

### **Fetch instruction** (short: FE)

- Pointer to next instruction from current program counter

- Load the instruction from memory

#### **Decode instruction (DE)**

- Get operands from register file

- Extend sign if needed

#### Fetch instruction (short: FE)

- Pointer to next instruction from current program counter

- Load the instruction from memory

#### **Decode instruction (DE)**

- Get operands from register file

- Extend sign if needed

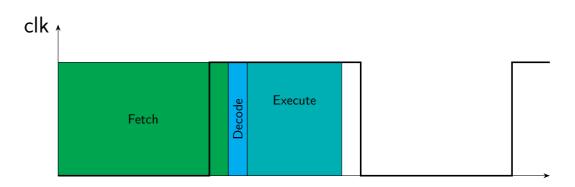

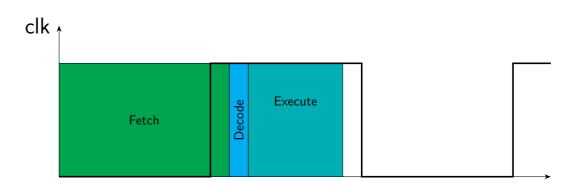

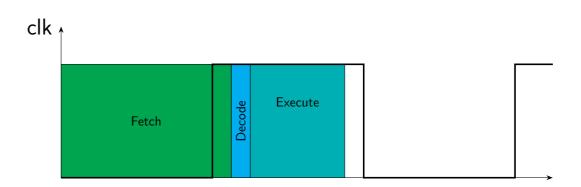

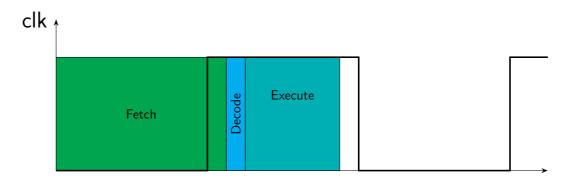

#### **Execute** (EX)

#### Fetch instruction (short: FE)

- Pointer to next instruction from current program counter

- Load the instruction from memory

#### **Decode instruction (DE)**

- Get operands from register file

- Extend sign if needed

#### **Execute** (EX)

ALU-Operation from instruction

### **Fetch instruction** (short: FE)

- Pointer to next instruction from current program counter

- Load the instruction from memory

#### **Decode instruction (DE)**

- Get operands from register file

- Extend sign if needed

### **Execute** (EX)

- ALU-Operation from instruction

- Calculate effective address

#### **Fetch instruction** (short: FE)

- Pointer to next instruction from current program counter

- Load the instruction from memory

#### **Decode instruction (DE)**

- Get operands from register file

- Extend sign if needed

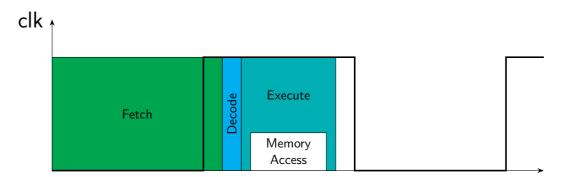

#### **Execute** (EX)

- ALU-Operation from instruction

- Calculate effective address

- Control flow: check condition

**Memory Access** (MA)

### Memory Access (MA)

• Reading or writing to memory

### Memory Access (MA)

- Reading or writing to memory

- optional

### Memory Access (MA)

- Reading or writing to memory

- optional

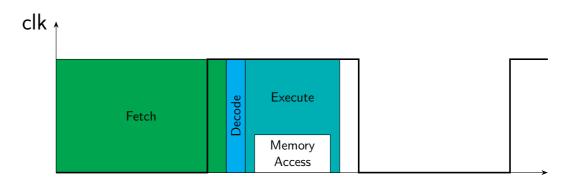

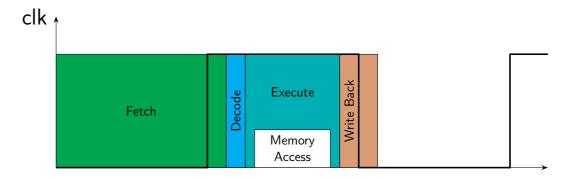

Write Back (WB)

### Memory Access (MA)

- Reading or writing to memory

- optional

### Write Back (WB)

Write result into destination register

### Memory Access (MA)

- Reading or writing to memory

- optional

#### Write Back (WB)

- Write result into destination register

- Commit new program counter

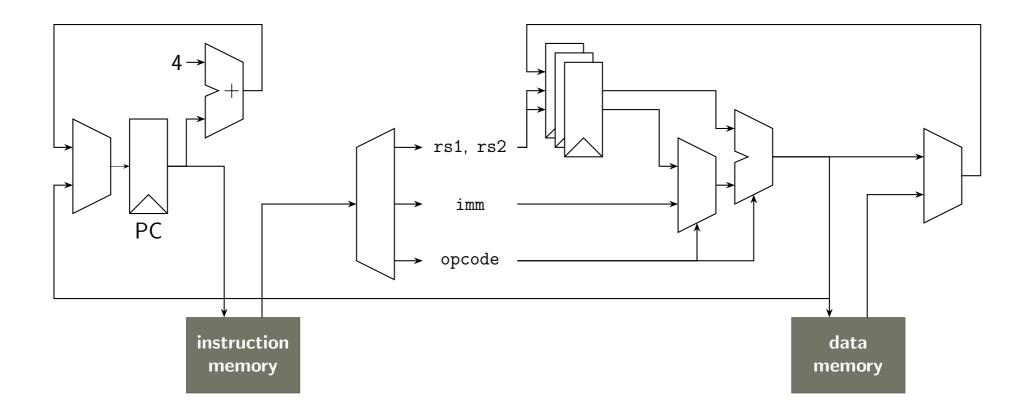

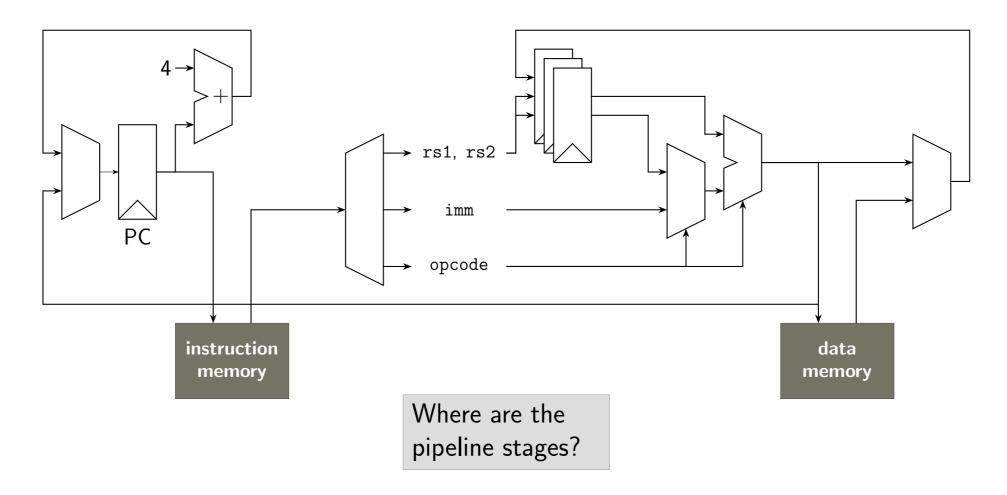

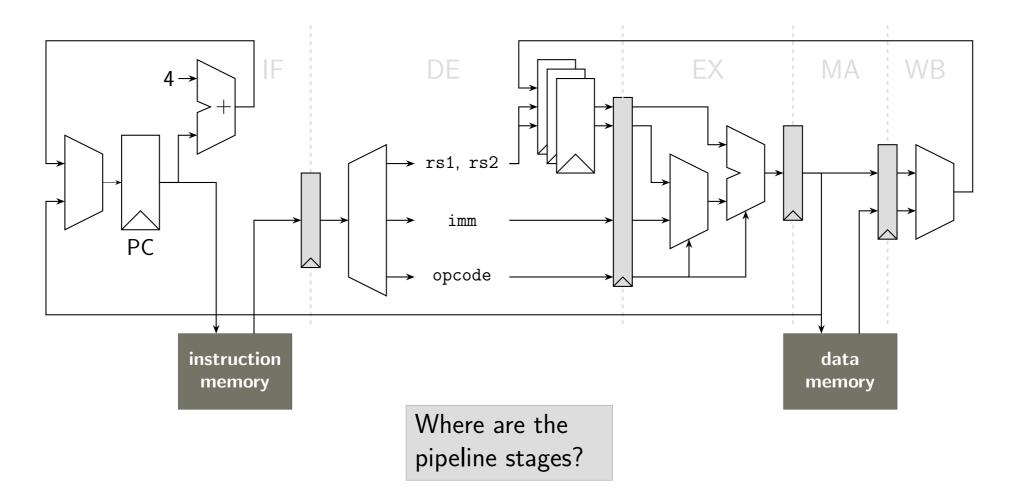

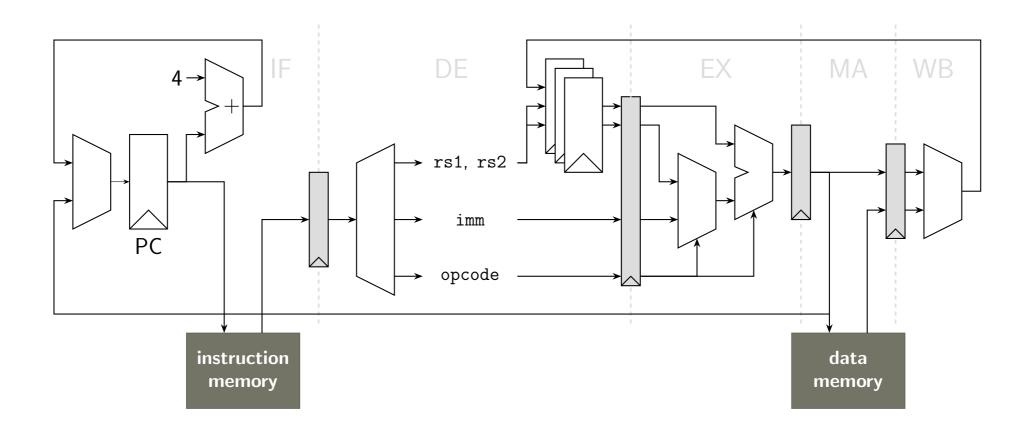

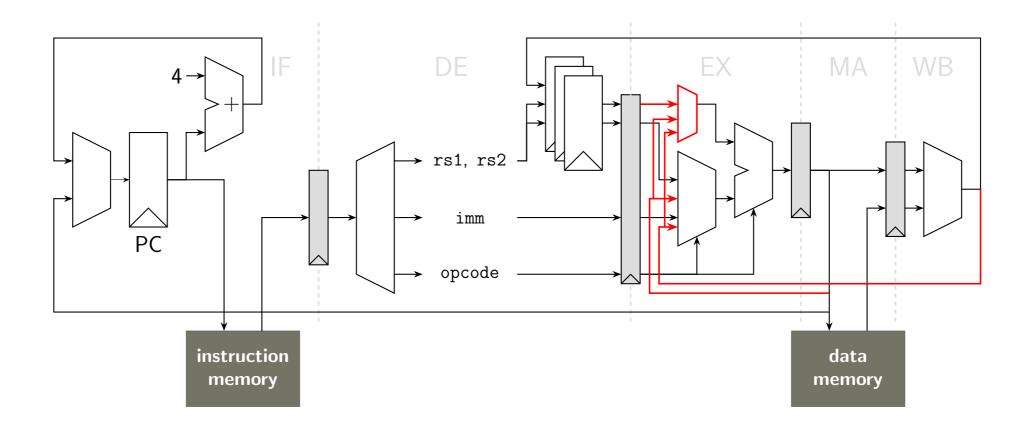

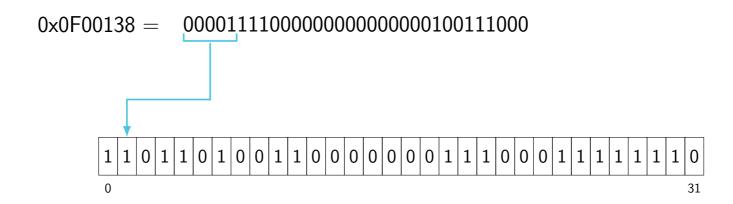

# Hardware Implementation (simplified)

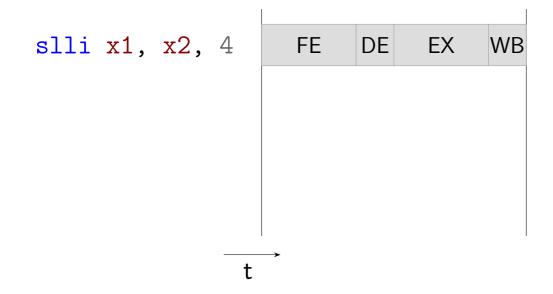

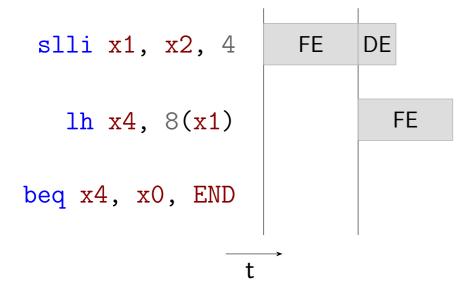

slli x1, x2, 4

t

t

$\stackrel{\longrightarrow}{\mathsf{t}}$

t

$\overrightarrow{t}$

```

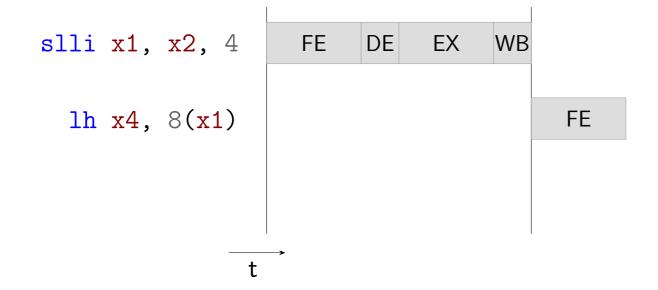

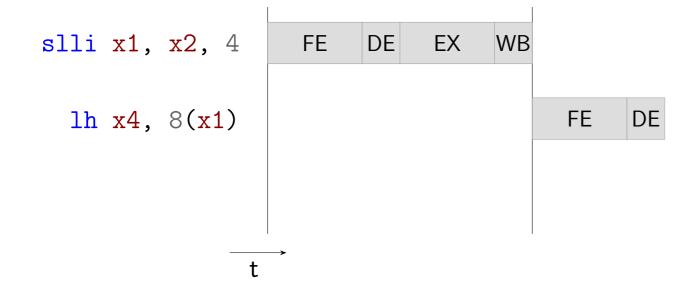

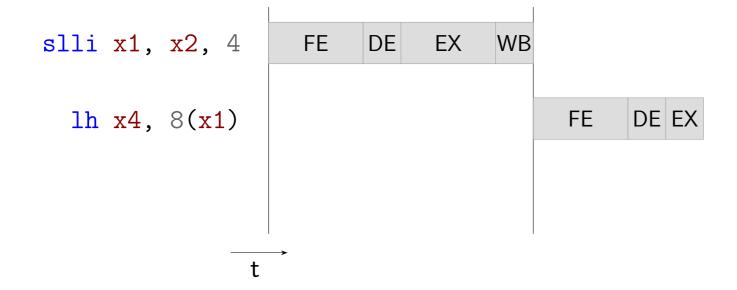

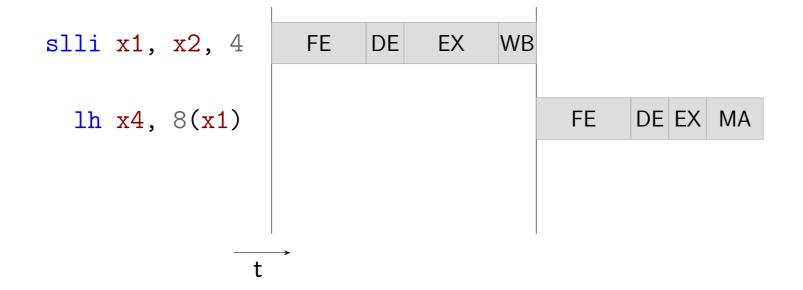

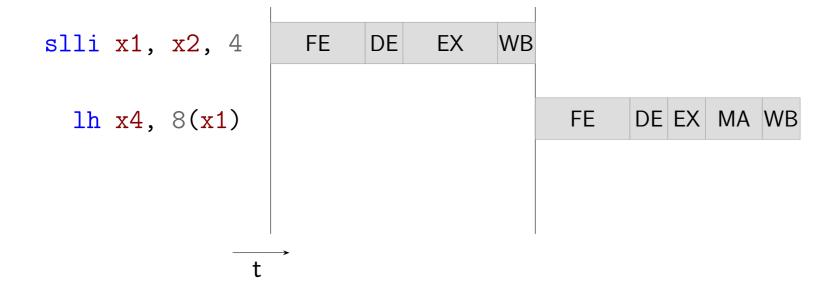

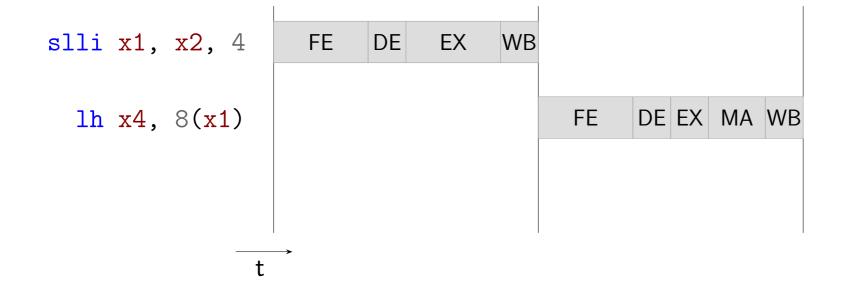

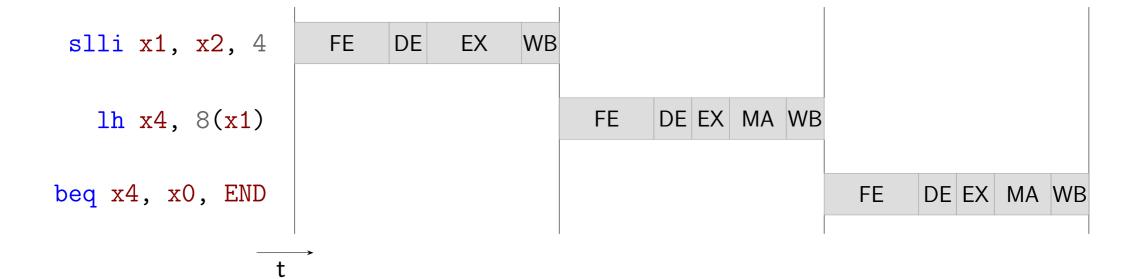

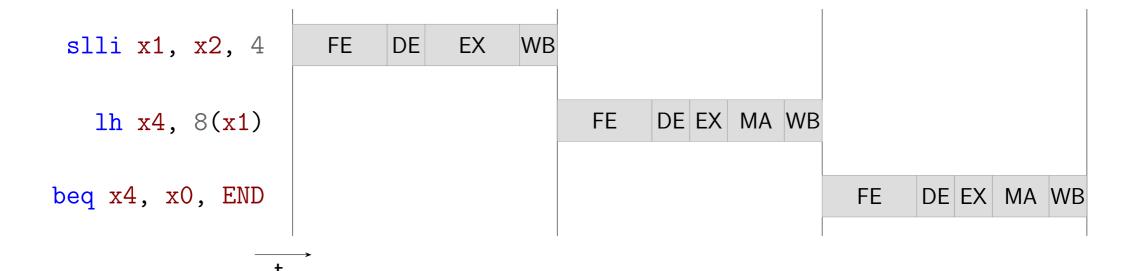

slli x1, x2, 4 FE DE EX WB

lh x4, 8(x1)

```

```

slli x1, x2, 4

FE DE EX WB

th x4, 8(x1)

FE DE EX MA WB

beq x4, x0, END

```

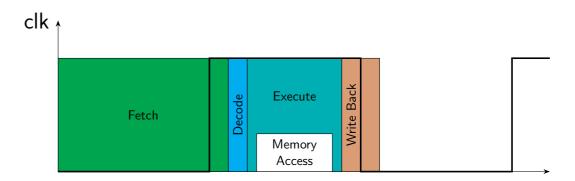

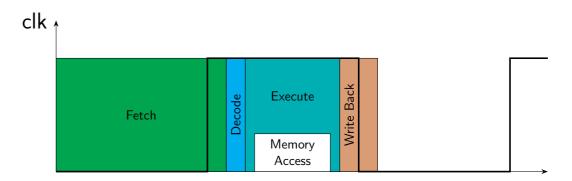

Can this be executed more efficiently?

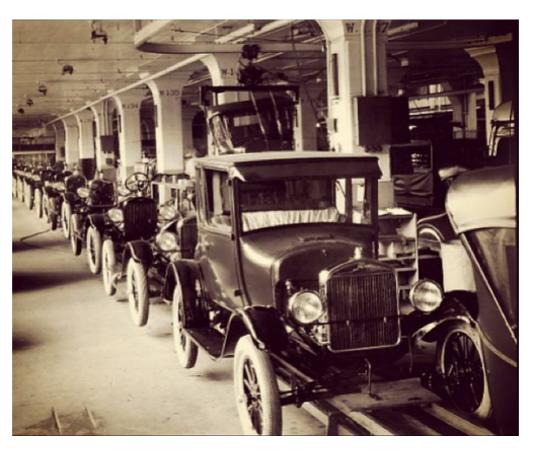

# **Inspiration: Assembly Line**

(c) BlueSpringsFordParts, CC BY 2.0

Overlapping execution of instructions

**Overlapping** execution of instructions

Start phase for next instruction once current completes phase

#### **Overlapping** execution of instructions

- Start phase for next instruction once current completes phase

- Parallelization of execution: Multiple concurrent instructions

#### **Overlapping** execution of instructions

- Start phase for next instruction once current completes phase

- Parallelization of execution: Multiple concurrent instructions

Pipeline stages are synchronized, handover at same time

#### **Overlapping** execution of instructions

- Start phase for next instruction once current completes phase

- Parallelization of execution: Multiple concurrent instructions

Pipeline stages are synchronized, handover at same time

Stage 0

#### **Overlapping** execution of instructions

- Start phase for next instruction once current completes phase

- Parallelization of execution: Multiple concurrent instructions

Pipeline stages are synchronized, handover at same time

Stage 0

Stage 1

#### **Overlapping** execution of instructions

- Start phase for next instruction once current completes phase

- Parallelization of execution: Multiple concurrent instructions

Pipeline stages are synchronized, handover at same time

Stage 0 Stage 1 Stage 2

#### **Overlapping** execution of instructions

- Start phase for next instruction once current completes phase

- Parallelization of execution: Multiple concurrent instructions

Pipeline stages are synchronized, handover at same time

Stage 0 Stage 1 Stage 2 Stage 3

#### **Overlapping** execution of instructions

- Start phase for next instruction once current completes phase

- Parallelization of execution: Multiple concurrent instructions

Pipeline stages are synchronized, handover at same time

Stage 3 Stage 4 Stage 0 Stage 2 Stage 1

#### **Overlapping** execution of instructions

- Start phase for next instruction once current completes phase

- Parallelization of execution: Multiple concurrent instructions

Pipeline stages are synchronized, handover at same time

Stage 0 Stage 4 Stage 2 Stage 3 Stage 1

Slowest stage determines clock frequency

#### **Overlapping** execution of instructions

- Start phase for next instruction once current completes phase

- Parallelization of execution: Multiple concurrent instructions

Pipeline stages are synchronized, handover at same time

Stage 0 Stage 1 Stage 2 Stage 3 Stage 4

Slowest stage determines clock frequency

Key technology for fast CPU implementations

# Hardware Implementation (simplified)

# Hardware Implementation (simplified)

```

slli x1, x2, 4

lh x4, 8(x1)

beq x4, x0, END

```

```

slli x1, x2, 4 FE

lh x4, 8(x1)

beq x4, x0, END

```

| slli x1, x2, 4  | FE       | DE |

|-----------------|----------|----|

| lh x4, 8(x1)    |          |    |

| beq x4, x0, END |          |    |

| t               | <b>→</b> |    |

| slli x1, x2, 4  | FE       | DE |

|-----------------|----------|----|

| lh x4, 8(x1)    |          | FE |

| beq x4, x0, END |          |    |

| t               | <b>→</b> |    |

| slli x1, x2, 4    | FE | DE | EX |  |  |  |

|-------------------|----|----|----|--|--|--|

| lh x4, 8(x1)      |    | FE | DE |  |  |  |

| beq x4, x0, END   |    |    | FE |  |  |  |

| $\xrightarrow{t}$ |    |    |    |  |  |  |

| slli x1, x2, 4  | FE       | DE | EX |    |

|-----------------|----------|----|----|----|

| lh x4, 8(x1)    |          | FE | DE | EX |

| beq x4, x0, END |          |    | FE | DE |

| t               | <b>→</b> | l  |    | I  |

| slli x1, x2, 4  | FE       | DE | EX |    | WB |

|-----------------|----------|----|----|----|----|

| lh x4, 8(x1)    |          | FE | DE | EX | MA |

| beq x4, x0, END |          |    | FE | DE | EX |

| t               | <b>→</b> | 1  | 1  | 1  | '  |

| slli x1, x2, 4  | FE       | DE | EX |    | WB |    |

|-----------------|----------|----|----|----|----|----|

| lh x4, 8(x1)    |          | FE | DE | EX | MA | WB |

| beq x4, x0, END |          |    | FE | DE | EX | MA |

| t               | <b>→</b> | l  | l  | l  |    |    |

| slli x1, x2, 4  | FE | DE | EX |    | WB |    |    |

|-----------------|----|----|----|----|----|----|----|

| lh x4, 8(x1)    |    | FE | DE | EX | MA | WB |    |

| beq x4, x0, END |    |    | FE | DE | EX | MA | WB |

| +               | →  | I  | I  | I  | 1  | I  | 1  |

| slli x1, x2, 4  | FE       | DE | EX | MA | WB |    |    |

|-----------------|----------|----|----|----|----|----|----|

| lh x4, 8(x1)    |          | FE | DE | EX | MA | WB |    |

| beq x4, x0, END |          |    | FE | DE | EX | MA | WB |

| t               | <b>→</b> |    |    |    |    |    |    |

| slli x1, x2, 4  | FE           | DE | EX | MA | WB |    |    |

|-----------------|--------------|----|----|----|----|----|----|

| lh x4, 8(x1)    |              | FE | DE | EX | MA | WB |    |

| beq x4, x0, END |              |    | FE | DE | EX | MA | WB |

| t               | <br><b>→</b> |    |    |    |    |    |    |

Problem: Instruction may need multiple cycles to complete stage

Problem: Instruction may need multiple cycles to complete stage

Next instruction is blocked → The IPC decreases

Problem: Instruction may need multiple cycles to complete stage

Next instruction is blocked → The IPC decreases

Example: Memory access that needs multiple cycles to complete (see lecture "memory")

Problem: Instruction may need multiple cycles to complete stage

Next instruction is blocked → The IPC decreases

Problem: Instruction may need multiple cycles to complete stage

Next instruction is blocked → The IPC decreases

| lh x4, 8(x1)   | FE |  |  |  |  |

|----------------|----|--|--|--|--|

| addi x2, x2, 4 |    |  |  |  |  |

Problem: Instruction may need multiple cycles to complete stage

Next instruction is blocked → The IPC decreases

Problem: Instruction may need multiple cycles to complete stage

Next instruction is blocked → The IPC decreases

| lh x4, 8(x1)   | FE | DE | EX |

|----------------|----|----|----|

| addi x2, x2, 4 |    | FE | DE |

Problem: Instruction may need multiple cycles to complete stage

Next instruction is blocked → The IPC decreases

| lh x4, 8(x1)   | FE | DE | EX | MA |  |

|----------------|----|----|----|----|--|

| addi x2, x2, 4 |    | FE | DE | EX |  |

Problem: Instruction may need multiple cycles to complete stage

Next instruction is blocked → The IPC decreases

| lh x4, 8(x1)   | FE | DE | EX | MA | MA |  |

|----------------|----|----|----|----|----|--|

| addi x2, x2, 4 |    | FE | DE | EX |    |  |

Problem: Instruction may need multiple cycles to complete stage

Next instruction is blocked → The IPC decreases

| lh x4, 8(x1)   | FE | DE | EX | MA | MA |

|----------------|----|----|----|----|----|

| addi x2, x2, 4 |    | FE | DE | EX | EX |

Problem: Instruction may need multiple cycles to complete stage

Next instruction is blocked → The IPC decreases

| lh x4, 8(x1)   | FE | DE | EX | MA | MA | WB |

|----------------|----|----|----|----|----|----|

| addi x2, x2, 4 |    | FE | DE | EX | EX | MA |

Problem: Instruction may need multiple cycles to complete stage

Next instruction is blocked → The IPC decreases

| lh x4, 8(x1)   | FE | DE | EX | MA | MA | WB |    |  |

|----------------|----|----|----|----|----|----|----|--|

|                |    |    |    |    |    |    |    |  |

| addi x2, x2, 4 |    | FE | DE | EX | EX | MA | WB |  |

|                |    |    |    |    |    |    |    |  |

Problem: Instruction may need multiple cycles to complete stage

Next instruction is blocked → The IPC decreases

Example: Memory access that needs multiple cycles to complete (see lecture "memory")

| lh x4, 8(x1)   | FE | DE | EX  | MA          | MA          | WB |    |

|----------------|----|----|-----|-------------|-------------|----|----|

|                |    |    | 5.5 | <b>-</b> >/ | <b>-</b> >/ |    | )  |

| addi x2, x2, 4 |    | FE | DE  | EX          | EX          | MA | WB |

Structural hazards can generally not be avoided!

In general, pipeline hazards are situations that block an instructions from entering the next pipeline stage

In general, pipeline hazards are situations that block an instructions from entering the next pipeline stage

• Structural hazards are resource conflicts due to hardware availability

In general, pipeline hazards are situations that block an instructions from entering the next pipeline stage

- Structural hazards are resource conflicts due to hardware availability

- Data hazards occur when a result of a previous command is not available

In general, pipeline hazards are situations that block an instructions from entering the next pipeline stage

- Structural hazards are resource conflicts due to hardware availability

- Data hazards occur when a result of a previous command is not available

- Control hazards are a result of changes in the control flow

In general, pipeline hazards are situations that block an instructions from entering the next pipeline stage

- Structural hazards are resource conflicts due to hardware availability

- Data hazards occur when a result of a previous command is not available

- Control hazards are a result of changes in the control flow

Hazards lead to a *pipeline stall* →IPC decreases

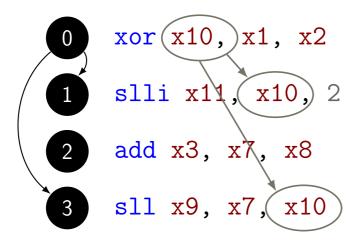

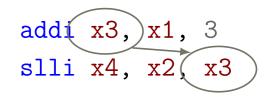

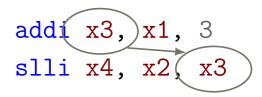

Problem: Conflict of operands between instructions

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

| xor x10, x1, x2  |  |  |  |  |

|------------------|--|--|--|--|

| slli x11, x10, 2 |  |  |  |  |

| add x3, x7, x8   |  |  |  |  |

| sll x9, x7, x10  |  |  |  |  |

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

| xor x10, x1, x2  | FE |  |  |  |

|------------------|----|--|--|--|

| slli x11, x10, 2 |    |  |  |  |

| add x3, x7, x8   |    |  |  |  |

| sll x9, x7, x10  |    |  |  |  |

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

| xor x10, x1, x2  | FE | DE |

|------------------|----|----|

| slli x11, x10, 2 |    | FE |

| add x3, x7, x8   |    |    |

| sll x9, x7, x10  |    |    |

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

| xor x10, x1, x2  | FE | DE | EX |

|------------------|----|----|----|

| slli x11, x10, 2 |    | FE | DE |

| add x3, x7, x8   |    |    | FE |

| sll x9, x7, x10  |    |    |    |

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

| xor x10, x1, x2  | FE | DE | EX | MA |

|------------------|----|----|----|----|

| slli x11, x10, 2 |    | FE | DE |    |

| add x3, x7, x8   |    |    | FE |    |

| sll x9, x7, x10  |    |    |    |    |

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

| xor x10, x1, x2  | FE | DE | EX | MA |

|------------------|----|----|----|----|

| slli x11, x10, 2 |    | FE | DE | DE |

| add x3, x7, x8   |    |    | FE |    |

| sll x9, x7, x10  |    |    |    |    |

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

| xor x10, x1, x2  | FE | DE | EX | MA |

|------------------|----|----|----|----|

| slli x11, x10, 2 |    | FE | DE | DE |

| add x3, x7, x8   |    |    | FE | FE |

| sll x9, x7, x10  |    |    |    |    |

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

| xor x10, x1, x2  | FE | DE | EX | MA | WB |

|------------------|----|----|----|----|----|

| slli x11, x10, 2 |    | FE | DE | DE |    |

| add x3, x7, x8   |    |    | FE | FE |    |

| sll x9, x7, x10  |    |    |    |    |    |

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

| <pre>xor x10, x1, x2</pre> | FE | DE | EX | MA | WB |

|----------------------------|----|----|----|----|----|

| slli x11, x10, 2           |    | FE | DE | DE | DE |

| add x3, x7, x8             |    |    | FE | FE | FE |

| sll x9, x7, x10            |    |    |    |    |    |

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

| <pre>xor x10, x1, x2</pre> | FE | DE | EX | MA | WB |    |

|----------------------------|----|----|----|----|----|----|

| slli x11, x10, 2           |    | FE | DE | DE | DE | EX |

| add x3, x7, x8             |    |    | FE | FE | FE |    |

| sll x9, x7, x10            |    |    |    |    |    |    |

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

| xor x10, x1, x2  | FE | DE | EX | MA | WB |    |  |

|------------------|----|----|----|----|----|----|--|

| slli x11, x10, 2 |    | FE | DE | DE | DE | EX |  |

| add x3, x7, x8   |    |    | FE | FE | FE | DE |  |

| sll x9, x7, x10  |    |    |    |    |    |    |  |

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

| xor x10, x1, x2  | FE | DE | EX | MA | WB |    |

|------------------|----|----|----|----|----|----|

| slli x11, x10, 2 |    | FE | DE | DE | DE | EX |

| add x3, x7, x8   |    |    | FE | FE | FE | DE |

| sll x9, x7, x10  |    |    |    |    |    | FE |

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

| xor x10, x1, x2  | FE | DE | EX | MA | WB |    |    |

|------------------|----|----|----|----|----|----|----|

| slli x11, x10, 2 |    | FE | DE | DE | DE | EX | MA |

| add x3, x7, x8   |    |    | FE | FE | FE | DE | EX |

| add AO, Ar, AO   |    |    |    |    |    |    |    |

| sll x9, x7, x10  |    |    |    |    |    | FE | DE |

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

| xor x10, x1, x2  | FE | DE | EX | MA | WB |    |    |      |

|------------------|----|----|----|----|----|----|----|------|

| slli x11, x10, 2 |    | FE | DE | DE | DE | EX | MA | WB   |

|                  |    |    | FE | FE | FE | DE | EX | MA   |

| add x3, x7, x8   |    |    | FL | FL | FL | DL | LA | IVIA |

| sll x9, x7, x10  |    |    |    |    |    | FE | DE | EX   |

Problem: Conflict of operands between instructions

Example: Need result of previous instruction

Result written in Writeback stage → Execution blocks until result becomes visible

| xor x10, x1, x2  | FE | DE | EX | MA | WB |    |    |    |

|------------------|----|----|----|----|----|----|----|----|

| slli x11, x10, 2 |    | FE | DE | DE | DE | EX | MA | WB |

| add x3, x7, x8   |    |    | FE | FE | FE | DE | EX | MA |

| sll x9, x7, x10  |    |    |    |    |    | FE | DE | EX |

How can we avoid the problem?

Instruction stream is sequentially stored in memory

Instruction stream is sequentially stored in memory

But:

Instruction stream is sequentially stored in memory

#### But:

• Can we reorder instructions?

Instruction stream is sequentially stored in memory

#### But:

- Can we reorder instructions?

- Can instructions be executed in parallel?

Instruction stream is sequentially stored in memory

#### But:

- Can we reorder instructions?

- Can instructions be executed in parallel?

Foundation of a large number of optimizations in computer architecture

Instruction stream is sequentially stored in memory

#### But:

- Can we reorder instructions?

- Can instructions be executed in parallel?

Foundation of a large number of optimizations in computer architecture

```

xor x10, x1, x2

slli x11, x10, 2

add x3, x7, x8

sll x9, x7, x10

```

Instruction stream is sequentially stored in memory

#### But:

- Can we reorder instructions?

- Can instructions be executed in parallel?

Foundation of a large number of optimizations in computer architecture

- 0 xor x10, x1, x2

- 1 slli x11, x10, 2

- 2 add x3, x7, x8

- 3 sll x9, x7, x10

Instruction stream is sequentially stored in memory

#### But:

- Can we reorder instructions?

- Can instructions be executed in parallel?

Foundation of a large number of optimizations in computer architecture

- 0 xor x10, x1, x2

- 1 slli x11, x10, 2

- 2 add x3, x7, x8

- 3 sll x9, x7, x10

Instruction stream is sequentially stored in memory

#### But:

- Can we reorder instructions?

- Can instructions be executed in parallel?

Foundation of a large number of optimizations in computer architecture

$$0 \quad xor(x10, x1, x2)$$

Instruction stream is sequentially stored in memory

#### But:

- Can we reorder instructions?

- Can instructions be executed in parallel?

Foundation of a large number of optimizations in computer architecture

- $0 \quad xor(x10,)x1, x2$

- 1 slli x11, x10, 2

- 2 add x3, x7, x8

- 3 sll x9, x7, x10

Instruction stream is sequentially stored in memory

#### But:

- Can we reorder instructions?

- Can instructions be executed in parallel?

Foundation of a large number of optimizations in computer architecture

Instruction stream is sequentially stored in memory

#### But:

- Can we reorder instructions?

- Can instructions be executed in parallel?

Foundation of a large number of optimizations in computer architecture

| xor x10, x1, x2  | 0 | FE |  |  |  |  |

|------------------|---|----|--|--|--|--|

| add x3, x7, x8   | 2 |    |  |  |  |  |

| slli x11, x10, 2 | 1 |    |  |  |  |  |

| sll x9, x7, x10  | 3 |    |  |  |  |  |

| xor x10, x1, x2  | 0 | FE | DE |  |  |

|------------------|---|----|----|--|--|

| add x3, x7, x8   | 2 |    | FE |  |  |

| slli x11, x10, 2 | 1 |    |    |  |  |

| sll x9, x7, x10  | 3 |    |    |  |  |

| <pre>xor x10, x1, x2</pre> | 0 | FE | DE | EX |

|----------------------------|---|----|----|----|

| add x3, x7, x8             | 2 |    | FE | DE |

| slli x11, x10, 2           |   |    |    | FE |

| sll x9, x7, x10            | 3 |    |    |    |

| < |

|---|

|   |

| Ξ |

|   |

| Ξ |

|   |

| <pre>xor x10, x1, x2</pre> | 0 | FE | DE | EX | MA | WB |

|----------------------------|---|----|----|----|----|----|

| add x3, x7, x8             | 2 |    | FE | DE | EX | MA |

| slli x11, x10, 2           | 1 |    |    | FE | DE | DE |

| sll x9, x7, x10            | 3 |    |    |    | FE | FE |

| <pre>xor x10, x1, x2</pre> | 0 | FE | DE | EX | MA | WB |    |

|----------------------------|---|----|----|----|----|----|----|

| add x3, x7, x8             | 2 |    | FE | DE | EX | MA | WB |

| slli x11, x10, 2           |   |    |    | FE | DE | DE | EX |

| sll x9, x7, x10            | 3 |    |    |    | FE | FE | DE |

| xor x10, x1, x2 0 | FE | DE | EX | MA | WB |    |    |

|-------------------|----|----|----|----|----|----|----|

| add x3, x7, x8 2  |    | FE | DE | EX | MA | WB |    |

| slli x11, x10, 2  |    |    | FE | DE | DE | EX | MA |

| sll x9, x7, x10 3 |    |    |    | FE | FE | DE | EX |

| <pre>xor x10, x1, x2</pre> | 0 | FE | DE | EX | MA | WB |    |    |    |

|----------------------------|---|----|----|----|----|----|----|----|----|

| add x3, x7, x8             | 2 |    | FE | DE | EX | MA | WB |    |    |

| <b>slli</b> x11, x10, 2    | 1 |    |    | FE | DE | DE | EX | MA | WB |

| sll x9, x7, x10            | 3 |    |    |    | FE | FE | DE | EX | MA |

Reorder instruction so that the data hazard is resolved

| xor x10, x1, x2  | 0 | FE | DE | EX | MA | WB |    |    |    |

|------------------|---|----|----|----|----|----|----|----|----|

| add x3, x7, x8   | 2 |    | FE | DE | EX | MA | WB |    |    |

| slli x11, x10, 2 | 1 |    |    | FE | DE | DE | EX | MA | WB |

| sll x9, x7, x10  | 3 |    |    |    | FE | FE | DE | EX | MA |

Reordering limited, especially with "deeper" (more stages) pipelines

Reordering instructions has limitations

Reordering instructions has limitations

| xor x10, x1, x2         | 0 |  |  |

|-------------------------|---|--|--|

| <b>slli</b> x11, x10, 2 | 1 |  |  |

| add x3, x7, x8          | 2 |  |  |

| sll x9, x7, x10         | 3 |  |  |

Reordering instructions has limitations

| xor x10, x1, x2 0  | FE |  |  |

|--------------------|----|--|--|

| slli x11, x10, 2 1 |    |  |  |

| add x3, x7, x8 2   |    |  |  |

| sll x9, x7, x10 3  |    |  |  |

Reordering instructions has limitations

| xor x10, x1, x2         | 0 | FE | DE |

|-------------------------|---|----|----|

| <b>slli</b> x11, x10, 2 | 1 |    | FE |

| add x3, x7, x8          | 2 |    |    |

| sll x9, x7, x10         | 3 |    |    |

Reordering instructions has limitations

| <pre>xor x10, x1, x2</pre> | 0 | FE | DE | EX |  |

|----------------------------|---|----|----|----|--|

| slli x11, x10, 2           | 1 |    | FE | DE |  |

| add x3, x7, x8             | 2 |    |    | FE |  |

| sll x9, x7, x10            | 3 |    |    |    |  |

Reordering instructions has limitations

| xor x10, x1, x2         | 0 | FE | DE | EX | MA |

|-------------------------|---|----|----|----|----|

| <b>slli</b> x11, x10, 2 | 1 |    | FE | DE | EX |

| add x3, x7, x8          | 2 |    |    | FE | DE |

| sll x9, x7, x10         | 3 |    |    |    | FE |

Reordering instructions has limitations

| <pre>xor x10, x1, x2</pre> | 0 | FE | DE | EX | MA | WB |

|----------------------------|---|----|----|----|----|----|

| slli x11, x10, 2           |   |    | FE | DE | EX | MA |

| add x3, x7, x8             |   |    |    | FE | DE | EX |

| sll x9, x7, x10            |   |    |    |    | FE | DE |

Reordering instructions has limitations

| xor x10, x1, x2 0 | FE | DE | EX | MA | WB |    |

|-------------------|----|----|----|----|----|----|

| slli x11, x10, 2  |    | FE | DE | EX | MA | WB |

| add x3, x7, x8 2  |    |    | FE | DE | EX | MA |

| sll x9, x7, x10 3 |    |    |    | FE | DE | EX |

Reordering instructions has limitations

| xor x10, x1, x2 0 | FE | DE | EX | MA | WB |    |    |

|-------------------|----|----|----|----|----|----|----|

| slli x11, x10, 2  |    | FE | DE | EX | MA | WB |    |

| add x3, x7, x8 2  |    |    | FE | DE | EX | MA | WB |

| sll x9, x7, x10 3 |    |    |    | FE | DE | EX | MA |

Reordering instructions has limitations

| xor x10, x1, x2  | 0 | FE | DE | EX | MA | WB |    |    |    |

|------------------|---|----|----|----|----|----|----|----|----|

| slli x11, x10, 2 | 1 |    | FE | DE | EX | MA | WB |    |    |

| add x3, x7, x8   | 2 |    |    | FE | DE | EX | MA | WB |    |

| sll x9, x7, x10  | 3 |    |    |    | FE | DE | EX | MA | WB |

# Pipeline Forwarding (simplified)

# Pipeline Forwarding (simplified)

# Data Hazard (continued)

# Data Hazard (continued)

Are we fine now?

```

lw x4, 8(x2)

addi x5, x4, 3

sll x6, x4, x5

andi x5, x6, 3

sw x5, 4(x2)

```

# Data Hazard (continued)

Are we fine now?

```

lw x4, 8(x2)

addi x5, x4, 3

sll x6, x4, x5

andi x5, x6, 3

sw x5, 4(x2)

```

#### There are other data dependencies

Compiler generates intermediate representation: instructions from code, variables as symbols

Compiler generates intermediate representation: instructions from code, variables as symbols

Example: Static Single Assignment Form (versions of variables)

```

int f(int *a, int b) {

return a[0]+a[1]+a[2]-b;

}

```

Compiler generates intermediate representation: instructions from code, variables as symbols

Example: Static Single Assignment Form (versions of variables)

```

int f(int *a, int b) {

return a[0]+a[1]+a[2]-b;

}

```

```

define i32 @f(i32* %0, i32 %1) #0 {

%3 = load i32, i32* %0, align 4

%4 = getelementptr inbounds i32, i32* %0, i64 1

%5 = load i32, i32* %4, align 4

%6 = getelementptr inbounds i32, i32* %0, i64 2

%7 = load i32, i32* %6, align 4

%8 = sub i32 %3, %1

%9 = add i32 %8, %5

%10 = add i32 %9, %7

ret i32 %10

}

```

Compiler generates intermediate representation: instructions from code, variables as symbols

Example: Static Single Assignment Form (versions of variables)

```

int f(int *a, int b) {

return a[0]+a[1]+a[2]-b;

}

define i32 @f(i32* %0, i32 %1) #0 {

%3 = load i32, i32* %0, align 4

%4 = getelementptr inbounds i32, i32* %0, i64 1

%5 = load i32, i32* %4, align 4

%6 = getelementptr inbounds i32, i32* %0, i64 2

%7 = load i32, i32* %6, align 4

%8 = sub i32 %3, %1

%9 = add i32 %8, %5

%10 = add i32 %9, %7

```

At this point we only have the data dependencies from above

ret i32 %10

### **Background: Register Allocation**

```

define i32 Of(i32* %0, i32 %1) #0 {

f:

%3 = load i32, i32* %0, align 4

lw

a2, 0(a0)

%4 = getelementptr inbounds i32, i32* %0, i64 1

\%5 = \text{load i32}, i32* \%4, align 4

a3, 4(a0)

%6 = getelementptr inbounds i32, i32* %0, i64 2

\%7 = \text{load i32}, \text{i32* \%6}, \text{align 4}

a0, 8(a0)

sub a1, a2, a1

\%8 = \text{sub i} 32 \%3, \%1

\%9 = add i32 \%8, \%5

add a1, a1, a3

%10 = add i32 \%9, \%7

addw a0, a0, a1

ret i32 %10

ret

```

Problem: Registers are scarce (RISC-V 31, minus ABI registers)

### **Background: Register Allocation**

Compiler generates machine code, unbound number of symbols must be mapped to registers

```

define i32 Of(i32* %0, i32 %1) #0 {

%3 = load i32, i32* %0, align 4

lw a2, 0(a0)

%4 = getelementptr inbounds i32, i32* %0, i64 1

\%5 = \text{load i32}, i32* \%4, align 4

a3, 4(a0)

\%6 = getelementptr inbounds i32, i32* \%0, i64 2

\%7 = \text{load i32}, \text{i32* \%6}, \text{align 4}

a0, 8(a0)

\%8 = \text{sub i} 32 \%3, \%1

sub a1, a2, a1

\%9 = add i32 \%8, \%5

add a1, a1, a3

%10 = add i32 \%9, \%7

addw a0, a0, a1

ret i32 %10

ret

```

Problem: Registers are scarce (RISC-V 31, minus ABI registers)

Limited availability of registers forces compiler to reuse registers, limits CPU optimizations

Limited availability of registers forces compiler to reuse registers, limits CPU optimizations

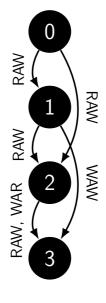

Read-After-Write dependency, also True Dependency

Limited availability of registers forces compiler to reuse registers, limits CPU optimizations

Read-After-Write dependency, also True Dependency

Dependency from before

Limited availability of registers forces compiler to reuse registers, limits CPU optimizations

Read-After-Write dependency, also True Dependency

- Dependency from before

- Mostly eliminated by forwarding

Limited availability of registers forces compiler to reuse registers, limits CPU optimizations

Read-After-Write dependency, also True Dependency

- Dependency from before

- Mostly eliminated by forwarding

Write-After-Read, also Anti-Dependency

Limited availability of registers forces compiler to reuse registers, limits CPU optimizations

Read-After-Write dependency, also True Dependency

- Dependency from before

- Mostly eliminated by forwarding

Write-After-Read, also Anti-Dependency

Register is used for another symbol versions

Limited availability of registers forces compiler to reuse registers, limits CPU optimizations

Read-After-Write dependency, also True Dependency

- Dependency from before

- Mostly eliminated by forwarding

Write-After-Read, also Anti-Dependency

- Register is used for another symbol versions

- Reordering would eliminate the required value

Limited availability of registers forces compiler to reuse registers, limits CPU optimizations

Read-After-Write dependency, also True Dependency

- Dependency from before

- Mostly eliminated by forwarding

Write-After-Read, also Anti-Dependency

- Register is used for another symbol versions

- Reordering would eliminate the required value

Write-After-Write, also Output Dependency

Limited availability of registers forces compiler to reuse registers, limits CPU optimizations

Read-After-Write dependency, also True Dependency

- Dependency from before

- Mostly eliminated by forwarding

Write-After-Read, also Anti-Dependency

- Register is used for another symbol versions

- Reordering would eliminate the required value

Write-After-Write, also Output Dependency

Register is used for another symbol versions

Limited availability of registers forces compiler to reuse registers, limits CPU optimizations

Read-After-Write dependency, also True Dependency

- Dependency from before

- Mostly eliminated by forwarding

Write-After-Read, also Anti-Dependency

- Register is used for another symbol versions

- Reordering would eliminate the required value

Write-After-Write, also Output Dependency

- Register is used for another symbol versions

- Reordering would switch values

Limited availability of registers forces compiler to reuse registers, limits CPU optimizations

Read-After-Write dependency, also True Dependency

- Dependency from before

- Mostly eliminated by forwarding

Write-After-Read, also Anti-Dependency

- Register is used for another symbol versions

- Reordering would eliminate the required value

Write-After-Write, also Output Dependency

- Register is used for another symbol versions

- Reordering would switch values

Read-after-Read is not a hazard

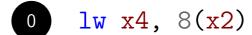

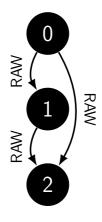

Data flow graph can be used to identify instruction level parallelism

Data flow graph can be used to identify instruction level parallelism Graph of data dependencies

Data flow graph can be used to identify instruction level parallelism

Graph of data dependencies

• Each instruction is a *vertex*

Data flow graph can be used to identify instruction level parallelism

- Each instruction is a *vertex*

- Each dependency is an edge

Data flow graph can be used to identify instruction level parallelism

- Each instruction is a *vertex*

- Each dependency is an edge

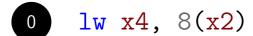

- 0 1w x4, 8(x2)

- 1 addi x5, x4, 3

- 2 sll x6, x4, x5

- 3 andi x5, x6, 3

- $4 \quad sw x5, 4(x2)$

Data flow graph can be used to identify instruction level parallelism

- Each instruction is a *vertex*

- Each dependency is an edge

- 0

- 1

- 2

- 3

- 4

- $0 \quad 1w \quad x4, \quad 8(x2)$

- 1 addi x5, x4, 3

- 2 sll x6, x4, x5

- 3 andi x5, x6, 3

- $4 \quad sw x5, 4(x2)$

Data flow graph can be used to identify instruction level parallelism

- Each instruction is a *vertex*

- Each dependency is an edge

- 1 addi x5, x4, 3

- 2 sll x6, x4, x5

- 3 andi x5, x6, 3

- $4 \quad sw x5, 4(x2)$

Data flow graph can be used to identify instruction level parallelism

- Each instruction is a *vertex*

- Each dependency is an edge

$$4 \quad sw x5, 4(x2)$$

Data flow graph can be used to identify instruction level parallelism

- Each instruction is a *vertex*

- Each dependency is an edge

$$4 \quad sw x5, 4(x2)$$

Data flow graph can be used to identify instruction level parallelism

- Each instruction is a *vertex*

- Each dependency is an edge

- 0 1w x4, 8(x2)

- 1 addi x5, x4, 3

- 2 sll x6, x4, x5

- 3 andi x5, x6, 3

- $4 \quad sw x5, 4(x2)$

Data flow graph can be used to identify instruction level parallelism

- Each instruction is a *vertex*

- Each dependency is an edge

- 0 1w x4, 8(x2)

- 1 addi x5, x4, 3

- 2 sll x6, x4, x5

- 3 andi x5, x6, 3

- $4 \quad sw x5, 4(x2)$

Data flow graph can be used to identify instruction level parallelism

- Each instruction is a *vertex*

- Each dependency is an edge

- 0 1w x4, 8(x2)

- 1 addi x5, x4, 3

- 2 sll x6, x4, x5

- 3 andi x5, x6, 3

- $4 \quad sw x5, 4(x2)$

So far: data dependencies, instructions are sequential

So far: data dependencies, instructions are sequential

So far: data dependencies, instructions are sequential

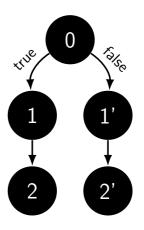

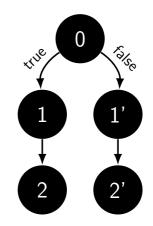

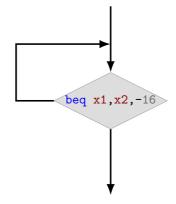

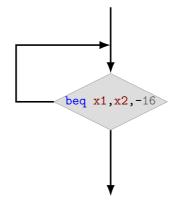

But they are not sequential:

Branch: Two possible "paths" in control flow

So far: data dependencies, instructions are sequential

- Branch: Two possible "paths" in control flow

- Which instruction to fetch next?

So far: data dependencies, instructions are sequential

- Branch: Two possible "paths" in control flow

- Which instruction to fetch next?

- Decision depends on EX stage

So far: data dependencies, instructions are sequential

- Branch: Two possible "paths" in control flow

- Which instruction to fetch next?

- Decision depends on EX stage

So far: data dependencies, instructions are sequential

But they are not sequential:

- Branch: Two possible "paths" in control flow

- Which instruction to fetch next?

- Decision depends on EX stage

Computer Architecture - Chapter 3 - CPU Pipelining

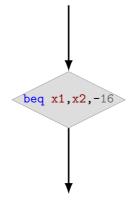

So far: data dependencies, instructions are sequential

- Branch: Two possible "paths" in control flow

- Which instruction to fetch next?

- Decision depends on EX stage

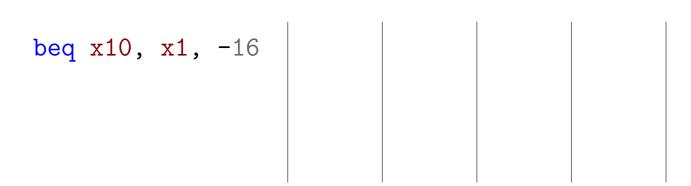

| beq | x10, | x1, | -16 | FE | DE |  |

|-----|------|-----|-----|----|----|--|

|     |      |     |     |    |    |  |

|     |      |     |     |    |    |  |

|     |      |     |     |    |    |  |

|  | 1 |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

So far: data dependencies, instructions are sequential

- Branch: Two possible "paths" in control flow

- Which instruction to fetch next?

- Decision depends on EX stage

| beq x10, x1, -16 | FE | DE | EX |

|------------------|----|----|----|

|                  |    |    |    |

|                  |    |    |    |

|                  |    |    |    |

| Kine | Salso 1 |

|------|---------|

|      |         |

| 2    | 2'      |

So far: data dependencies, instructions are sequential

- Branch: Two possible "paths" in control flow

- Which instruction to fetch next?

- Decision depends on EX stage

| beq x10, x1, -16 | FE | DE | EX | MA |

|------------------|----|----|----|----|

| slli x11, x10, 2 |    |    |    | FE |

|                  |    |    |    |    |

| True | Salso I |

|------|---------|

|      |         |

| 2    | 2'      |

So far: data dependencies, instructions are sequential

- Branch: Two possible "paths" in control flow

- Which instruction to fetch next?

- Decision depends on EX stage

| beq x10, x1, -16 | FE | DE | EX | MA | WB |    |    |    |

|------------------|----|----|----|----|----|----|----|----|

| slli x11, x10, 2 |    |    |    | FE | DE | EX | MA | WB |

| add x3, x7, x8   |    |    |    |    | FE | DE | EX | MA |

Recap: IPC of 1 is ideal

Recap: IPC of 1 is ideal

**RAW**: Fundamental impact

Recap: IPC of 1 is ideal

**RAW**: Fundamental impact

• Example: Every fourth instruction depends on result, penalty: 2 cycles

CPI =

Recap: IPC of 1 is ideal

**RAW**: Fundamental impact

• Example: Every fourth instruction depends on result, penalty: 2 cycles

CPI = 1

Recap: IPC of 1 is ideal

**RAW**: Fundamental impact

$$CPI = 1 + \frac{1}{4}$$

Recap: IPC of 1 is ideal

**RAW**: Fundamental impact

$$\mathsf{CPI} = 1 + \frac{1}{4} \cdot 2$$

Recap: IPC of 1 is ideal

**RAW**: Fundamental impact

$$CPI = 1 + \frac{1}{4} \cdot 2 \Rightarrow IPC =$$

Recap: IPC of 1 is ideal

**RAW**: Fundamental impact

$$CPI = 1 + \frac{1}{4} \cdot 2 \Rightarrow IPC = \frac{1}{CPI}$$

Recap: IPC of 1 is ideal

**RAW**: Fundamental impact

$$CPI = 1 + \frac{1}{4} \cdot 2 \Rightarrow IPC = \frac{1}{CPI} = \frac{1}{1 + \frac{1}{4} \cdot 2}$$

Recap: IPC of 1 is ideal

**RAW**: Fundamental impact

$$CPI = 1 + \frac{1}{4} \cdot 2 \Rightarrow IPC = \frac{1}{CPI} = \frac{1}{1 + \frac{1}{4} \cdot 2} = \frac{2}{3}$$

Recap: IPC of 1 is ideal

**RAW**: Fundamental impact

• Example: Every fourth instruction depends on result, penalty: 2 cycles

$$CPI = 1 + \frac{1}{4} \cdot 2 \Rightarrow IPC = \frac{1}{CPI} = \frac{1}{1 + \frac{1}{4} \cdot 2} = \frac{2}{3}$$

Nearly entirely solved by forwarding

Recap: IPC of 1 is ideal

**RAW**: Fundamental impact

• Example: Every fourth instruction depends on result, penalty: 2 cycles

$$CPI = 1 + \frac{1}{4} \cdot 2 \Rightarrow IPC = \frac{1}{CPI} = \frac{1}{1 + \frac{1}{4} \cdot 2} = \frac{2}{3}$$

Nearly entirely solved by forwarding

**WAW** and **WAR**: Result from register allocation

Recap: IPC of 1 is ideal

**RAW**: Fundamental impact

Example: Every fourth instruction depends on result, penalty: 2 cycles

$$CPI = 1 + \frac{1}{4} \cdot 2 \Rightarrow IPC = \frac{1}{CPI} = \frac{1}{1 + \frac{1}{4} \cdot 2} = \frac{2}{3}$$

Nearly entirely solved by forwarding

WAW and WAR: Result from register allocation

• For simple pipeline they are not important, but limit optimizations (see part 4)

Recap: IPC of 1 is ideal

**RAW**: Fundamental impact

• Example: Every fourth instruction depends on result, penalty: 2 cycles

$$CPI = 1 + \frac{1}{4} \cdot 2 \Rightarrow IPC = \frac{1}{CPI} = \frac{1}{1 + \frac{1}{4} \cdot 2} = \frac{2}{3}$$

Nearly entirely solved by forwarding

WAW and WAR: Result from register allocation

• For simple pipeline they are not important, but limit optimizations (see part 4)

Control Hazards: Many branches, impact considerably height

Recap: IPC of 1 is ideal

**RAW**: Fundamental impact

Example: Every fourth instruction depends on result, penalty: 2 cycles

$$CPI = 1 + \frac{1}{4} \cdot 2 \Rightarrow IPC = \frac{1}{CPI} = \frac{1}{1 + \frac{1}{4} \cdot 2} = \frac{2}{3}$$

Nearly entirely solved by forwarding

WAW and WAR: Result from register allocation

• For simple pipeline they are not important, but limit optimizations (see part 4)

Control Hazards: Many branches, impact considerably height

• Waiting for decision is penalty, can we guess it? (remain of this part)

Goal: Bring IPC up (near to one or even above)

Goal: Bring IPC up (near to one or even above)

Speculative Execution

Goal: Bring IPC up (near to one or even above)

Speculative Execution

Branch prediction: Reduce the impact of branch decisions

Goal: Bring IPC up (near to one or even above)

Speculative Execution

- Branch prediction: Reduce the impact of branch decisions

- Other kinds of speculation: Address, data, ...

Goal: Bring IPC up (near to one or even above)

Speculative Execution

- Branch prediction: Reduce the impact of branch decisions

- Other kinds of speculation: Address, data, ...

Parallelism

Goal: Bring IPC up (near to one or even above)

#### Speculative Execution

- Branch prediction: Reduce the impact of branch decisions

- Other kinds of speculation: Address, data, ...

#### Parallelism

Instruction Level Parallelism (ILP)

Goal: Bring IPC up (near to one or even above)

#### Speculative Execution

- Branch prediction: Reduce the impact of branch decisions

- Other kinds of speculation: Address, data, ...

#### Parallelism

- Instruction Level Parallelism (ILP)

- Pipelining

Goal: Bring IPC up (near to one or even above)

### Speculative Execution

- Branch prediction: Reduce the impact of branch decisions

- Other kinds of speculation: Address, data, ...

- Instruction Level Parallelism (ILP)

- Pipelining

- ► Superscalar execution, out-of-order execution (lecture part 4)

Goal: Bring IPC up (near to one or even above)

### Speculative Execution

- Branch prediction: Reduce the impact of branch decisions

- Other kinds of speculation: Address, data, ...

- Instruction Level Parallelism (ILP)

- Pipelining

- ► Superscalar execution, out-of-order execution (lecture part 4)

- Data parallelism

Goal: Bring IPC up (near to one or even above)

### Speculative Execution

- Branch prediction: Reduce the impact of branch decisions

- Other kinds of speculation: Address, data, ...

- Instruction Level Parallelism (ILP)

- Pipelining

- ► Superscalar execution, out-of-order execution (lecture part 4)

- Data parallelism

- Data vectors, single instruction multiple data

Goal: Bring IPC up (near to one or even above)

### Speculative Execution

- Branch prediction: Reduce the impact of branch decisions

- Other kinds of speculation: Address, data, ...

- Instruction Level Parallelism (ILP)

- Pipelining

- ► Superscalar execution, out-of-order execution (lecture part 4)

- Data parallelism

- Data vectors, single instruction multiple data

- Thread parallelism

Goal: Bring IPC up (near to one or even above)

### Speculative Execution

- Branch prediction: Reduce the impact of branch decisions

- Other kinds of speculation: Address, data, ...

- Instruction Level Parallelism (ILP)

- Pipelining

- ► Superscalar execution, out-of-order execution (lecture part 4)

- Data parallelism

- Data vectors, single instruction multiple data

- Thread parallelism

- Execution of multiple different instruction streams

Branches are problematic for pipelining

Branches are problematic for pipelining

Decision delayed until EX stage

Branches are problematic for pipelining

- Decision delayed until EX stage

- Stall pipeline until decision made → IPC goes down

Branches are problematic for pipelining

- Decision delayed until EX stage

- Stall pipeline until decision made → IPC goes down

Branch predition:

Branches are problematic for pipelining

- Decision delayed until EX stage

- Stall pipeline until decision made → IPC goes down

### Branch predition:

Execute one of the paths speculatively

### Branches are problematic for pipelining

- Decision delayed until EX stage

### Branch predition:

- Execute one of the paths speculatively

- Withdraw execution if decision is different to speculation

### Branches are problematic for pipelining

- Decision delayed until EX stage

- Stall pipeline until decision made → IPC goes down

### Branch predition:

- Execute one of the paths speculatively

- Withdraw execution if decision is different to speculation

Impact on IPC:

Computer Architecture – Chapter 3 – CPU Pipelining

### Branches are problematic for pipelining

- Decision delayed until EX stage

- Stall pipeline until decision made → IPC goes down

### Branch predition:

- Execute one of the paths speculatively

- Withdraw execution if decision is different to speculation

### Impact on IPC:

IPC=1 if we always select the right path

### Branches are problematic for pipelining

- Decision delayed until EX stage

- Stall pipeline until decision made → IPC goes down

### Branch predition:

- Execute one of the paths speculatively

- Withdraw execution if decision is different to speculation

### Impact on IPC:

- IPC=1 if we always select the right path

- IPC<1 if we select wrong path, misprediction penalty

### Branches are problematic for pipelining

- Decision delayed until EX stage

- Stall pipeline until decision made → IPC goes down

### Branch predition:

- Execute one of the paths speculatively

- Withdraw execution if decision is different to speculation

### Impact on IPC:

- IPC=1 if we always select the right path

- IPC<1 if we select wrong path, misprediction penalty

Problem: Which path to predict?

M

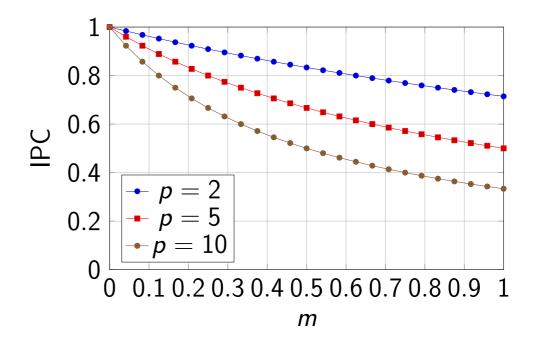

### **Parameters**

• b: Branch rate (relative number of branch instructions)

- b: Branch rate (relative number of branch instructions)

- *m*: Misprediction rate (how many of branches are wrongly predicted)

- b: Branch rate (relative number of branch instructions)

- *m*: Misprediction rate (how many of branches are wrongly predicted)

- p: Penalty for mispredicts (extra cycles to flush pipeline)

#### Parameters

- b: Branch rate (relative number of branch instructions)

- m: Misprediction rate (how many of branches are wrongly predicted)

- p: Penalty for mispredicts (extra cycles to flush pipeline)

IPC =

- b: Branch rate (relative number of branch instructions)

- m: Misprediction rate (how many of branches are wrongly predicted)

- p: Penalty for mispredicts (extra cycles to flush pipeline)

- b: Branch rate (relative number of branch instructions)

- m: Misprediction rate (how many of branches are wrongly predicted)

- p: Penalty for mispredicts (extra cycles to flush pipeline)

$$IPC = \frac{1}{1}$$

- b: Branch rate (relative number of branch instructions)

- m: Misprediction rate (how many of branches are wrongly predicted)

- p: Penalty for mispredicts (extra cycles to flush pipeline)

$$IPC = \frac{1}{1+b}$$

- b: Branch rate (relative number of branch instructions)

- m: Misprediction rate (how many of branches are wrongly predicted)

- p: Penalty for mispredicts (extra cycles to flush pipeline)

$$\mathsf{IPC} = \frac{1}{1 + b \cdot m}$$

- b: Branch rate (relative number of branch instructions)

- m: Misprediction rate (how many of branches are wrongly predicted)

- p: Penalty for mispredicts (extra cycles to flush pipeline)

$$\mathsf{IPC} = \frac{1}{1 + b \cdot m \cdot p}$$

- b: Branch rate (relative number of branch instructions)

- *m*: Misprediction rate (how many of branches are wrongly predicted)

- p: Penalty for mispredicts (extra cycles to flush pipeline)

$$IPC = \frac{1}{1 + b \cdot m \cdot p}$$

### **Avoid Branches**

Replace branch instructions with other instructions

### **Avoid Branches**

Replace branch instructions with other instructions

#### **Avoid Branches**

Replace branch instructions with other instructions

### **Predict Branches**

The deeper the pipeline, the more expensive (lower IPC) mispredicts become

#### **Avoid Branches**

Replace branch instructions with other instructions

- The deeper the pipeline, the more expensive (lower IPC) mispredicts become

- Increasing the rate of correct predictions has significant impact

#### **Avoid Branches**

Replace branch instructions with other instructions

- The deeper the pipeline, the more expensive (lower IPC) mispredicts become

- Increasing the rate of correct predictions has significant impact

- Two types of branch prediction

#### **Avoid Branches**

Replace branch instructions with other instructions

- The deeper the pipeline, the more expensive (lower IPC) mispredicts become

- Increasing the rate of correct predictions has significant impact

- Two types of branch prediction

- Static branch prediction: Only use information at hand

#### **Avoid Branches**

Replace branch instructions with other instructions

- The deeper the pipeline, the more expensive (lower IPC) mispredicts become

- Increasing the rate of correct predictions has significant impact

- Two types of branch prediction

- Static branch prediction: Only use information at hand

- Dynamich branch prediction: Keep book about previous decisions

## **Conditional instructions**

### **Conditional instructions**

• Instructions that are only executed based on flag, see part 2

### **Conditional instructions**

- Instructions that are only executed based on flag, see part 2

- Not in RISC-V, example ARM:

### **Conditional instructions**

- Instructions that are only executed based on flag, see part 2

- Not in RISC-V, example ARM:

Modify code, example loop unrolling

### **Conditional instructions**

- Instructions that are only executed based on flag, see part 2

- Not in RISC-V, example ARM:

## Modify code, example loop unrolling

Rewrite loops in repeating code sequences

#### **Conditional instructions**

- Instructions that are only executed based on flag, see part 2

- Not in RISC-V, example ARM:

## Modify code, example loop unrolling

- Rewrite loops in repeating code sequences

- Reduces number of branches, but increases code size

#### **Conditional instructions**

- Instructions that are only executed based on flag, see part 2

- Not in RISC-V, example ARM:

## Modify code, example loop unrolling

- Rewrite loops in repeating code sequences

- Reduces number of branches, but increases code size

- This is most often done by the compiler (inner loops, few iterations)

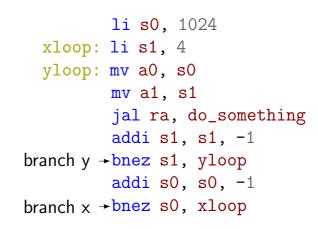

# **Loop Unrolling**

# **Loop Unrolling**

```

Example: 3 nested loops

```

```

for (int i=0; i<3; i++)

for (int j=0; j<3; j++)

for (int k=0; k<3; k++)

Z[i][j] += X[i][k] * Y[k][j];</pre>

```

# **Loop Unrolling**

```

Example: 3 nested loops

```

```

for (int i=0; i<3; i++)

for (int j=0; j<3; j++)

for (int k=0; k<3; k++)

Z[i][j] += X[i][k] * Y[k][j];</pre>

```

### Loop unrolling of most inner loop:

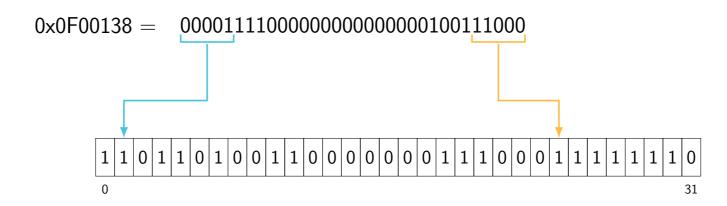

Predict if branch is taken or not solely based on the instruction

Predict if branch is taken or not solely based on the instruction

Predict if branch is taken or not solely based on the instruction

User-controlled

Use a bit in opcode to indicate if branch is probable

Predict if branch is taken or not solely based on the instruction

- Use a bit in opcode to indicate if branch is probable

- Generally useful for loop counters

Predict if branch is taken or not solely based on the instruction

- Use a bit in opcode to indicate if branch is probable

- Generally useful for loop counters

- Examples in: PowerPC, Alpha, MMIX

Predict if branch is taken or not solely based on the instruction

- Use a bit in opcode to indicate if branch is probable

- Generally useful for loop counters

- Examples in: PowerPC, Alpha, MMIX

- Not in RISC-V: Coding space is too precious and the result is not better than what hardware-based branch prediction (remain of this part) can achieve

Predict if branch is taken or not solely based on the instruction

#### User-controlled

- Use a bit in opcode to indicate if branch is probable

- Generally useful for loop counters

- Examples in: PowerPC, Alpha, MMIX

- Not in RISC-V: Coding space is too precious and the result is not better than what hardware-based branch prediction (remain of this part) can achieve

Machine decision

Predict if branch is taken or not solely based on the instruction

#### User-controlled

- Use a bit in opcode to indicate if branch is probable

- Generally useful for loop counters

- Examples in: PowerPC, Alpha, MMIX

- Not in RISC-V: Coding space is too precious and the result is not better than what hardware-based branch prediction (remain of this part) can achieve

#### Machine decision

Predict based on inspection of the instruction

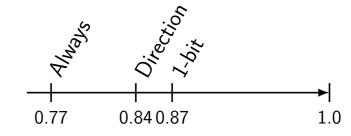

Observation: Probability of branch taken is 60-70%

Observation: Probability of branch taken is 60-70%

Idea: Always predict the jump

Observation: Probability of branch taken is 60-70%

Idea: Always predict the jump

Assumptions:

Observation: Probability of branch taken is 60-70%

Idea: Always predict the jump

## Assumptions:

• 20% of instructions are branches

Observation: Probability of branch taken is 60-70%

Idea: Always predict the jump

## Assumptions:

- 20% of instructions are branches

- 70% of branches are taken

Observation: Probability of branch taken is 60-70%

Idea: Always predict the jump

### Assumptions:

- 20% of instructions are branches

- 70% of branches are taken

- Misprediction penalty: 5 cycles (realistic for 11-15 stage pipeline)

Observation: Probability of branch taken is 60-70%

Idea: Always predict the jump

### Assumptions:

- 20% of instructions are branches

- 70% of branches are taken

- Misprediction penalty: 5 cycles (realistic for 11-15 stage pipeline)

What is the IPC?

Observation: Probability of branch taken is 60-70%

Idea: Always predict the jump

### Assumptions:

- 20% of instructions are branches

- 70% of branches are taken

- Misprediction penalty: 5 cycles (realistic for 11-15 stage pipeline)

What is the IPC?

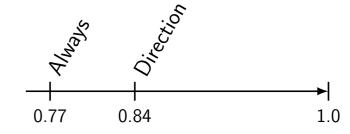

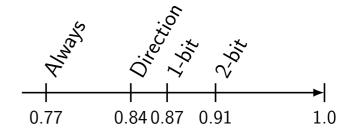

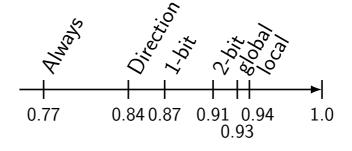

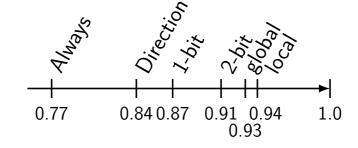

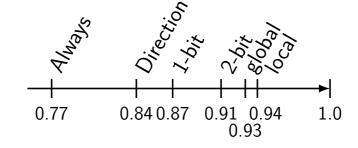

$$\mathsf{IPC} = \frac{1}{1 + 0.2 \cdot (1 - 0.7) \cdot 5} = \frac{1}{1.3} = 0.77$$

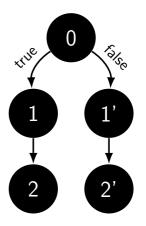

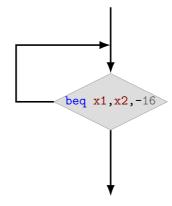

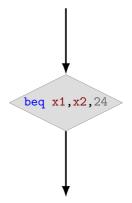

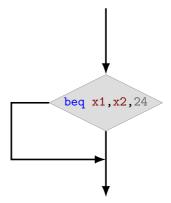

Look closer at branches

Look closer at branches

Observation: Differences by branch direction

Computer Architecture - Chapter 3 - CPU Pipelining

Look closer at branches

Observation: Differences by branch direction

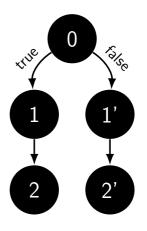

### **Backward branch**

Look closer at branches

Observation: Differences by branch direction

### **Backward branch**

Look closer at branches

Observation: Differences by branch direction

### **Backward branch**

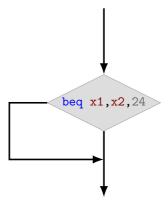

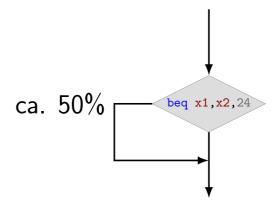

#### **Forward branch**

Look closer at branches

Observation: Differences by branch direction

### **Backward branch**

#### **Forward branch**

## **Static Branch Prediction: Direction**

Look closer at branches

Observation: Differences by branch direction

#### **Backward branch**

#### **Forward branch**

## **Static Branch Prediction: Direction**

Look closer at branches

Observation: Differences by branch direction

#### **Backward branch**

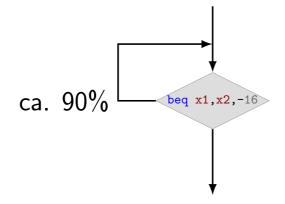

# ca. 90% beq x1,x2,-16

#### Forward branch

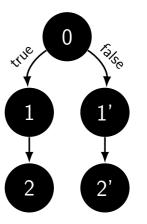

Assumptions:

## Assumptions:

• 80% of branches are backwards branches

## Assumptions:

- 80% of branches are backwards branches

- Branch taken 90%/50% for backward/forward branch

## Assumptions:

- 80% of branches are backwards branches

- Branch taken 90%/50% for backward/forward branch

Impact on IPC:

CPI =

## Assumptions:

- 80% of branches are backwards branches

- Branch taken 90%/50% for backward/forward branch

$$CPI = 1 +$$

## Assumptions:

- 80% of branches are backwards branches

- Branch taken 90%/50% for backward/forward branch

$$CPI = 1 + 0.2 \cdot$$

## Assumptions:

- 80% of branches are backwards branches

- Branch taken 90%/50% for backward/forward branch

$$\mathsf{CPI} = 1 + 0.2 \cdot \ 0.8 \cdot (1 - 0.9)$$

## Assumptions:

- 80% of branches are backwards branches

- Branch taken 90%/50% for backward/forward branch

$$\mathsf{CPI} = 1 + 0.2 \cdot (0.8 \cdot (1 - 0.9) + 0.2 \cdot (1 - 0.5))$$

## Assumptions:

- 80% of branches are backwards branches

- Branch taken 90%/50% for backward/forward branch

$$\mathsf{CPI} = 1 + 0.2 \cdot (0.8 \cdot (1 - 0.9) + 0.2 \cdot (1 - 0.5)) \cdot 5$$

#### Assumptions:

- 80% of branches are backwards branches

- Branch taken 90%/50% for backward/forward branch

$$\mathsf{CPI} = 1 + 0.2 \cdot (0.8 \cdot (1 - 0.9) + 0.2 \cdot (1 - 0.5)) \cdot 5 = 1,18$$

## Assumptions:

- 80% of branches are backwards branches

- Branch taken 90%/50% for backward/forward branch

$$\mathsf{CPI} = 1 + 0.2 \cdot (0.8 \cdot (1 - 0.9) + 0.2 \cdot (1 - 0.5)) \cdot 5 = 1,18$$

$$IPC = \frac{1}{CPI} = 0,84$$

## Assumptions:

- 80% of branches are backwards branches

- Branch taken 90%/50% for backward/forward branch

$$\mathsf{CPI} = 1 + 0.2 \cdot (0.8 \cdot (1 - 0.9) + 0.2 \cdot (1 - 0.5)) \cdot 5 = 1,18$$

$$IPC = \frac{1}{CPI} = 0,84$$

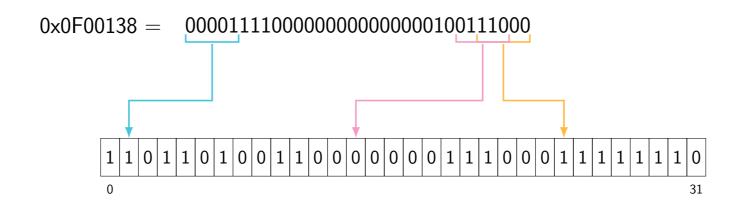

Observation: Static branch prediction works well, but not for forward branch

Observation: Static branch prediction works well, but not for forward branch

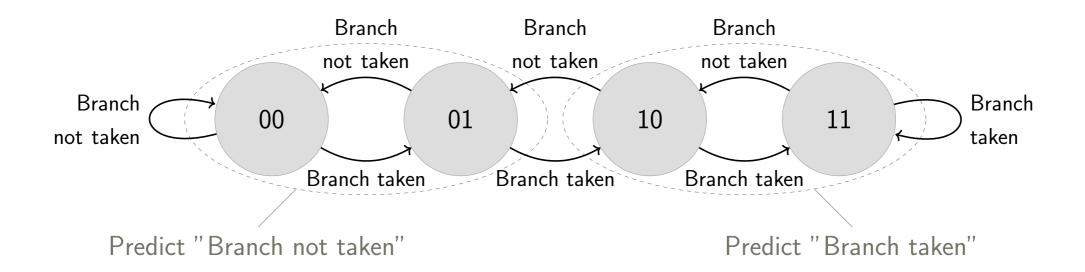

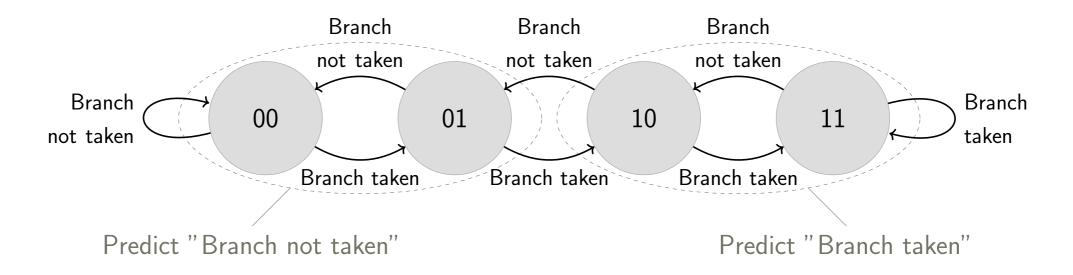

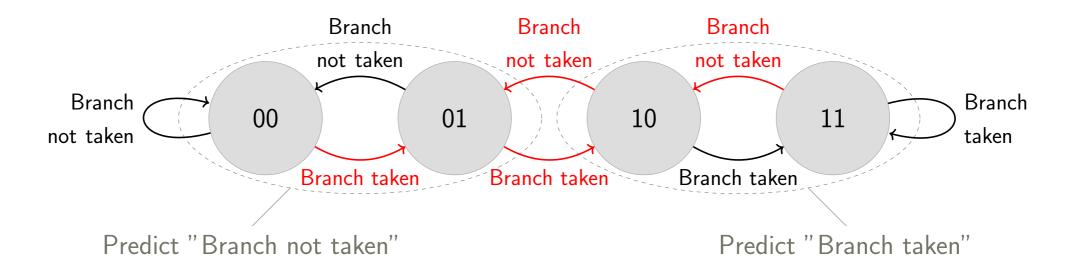

Approach: Branch prediction depends on history

Observation: Static branch prediction works well, but not for forward branch

Approach: Branch prediction depends on *history*

Based on correlations

Observation: Static branch prediction works well, but not for forward branch

Approach: Branch prediction depends on history

#### Based on correlations

Temporal correlation

If a branch was taken recently, it will probably be taken again (loops, etc.)

Observation: Static branch prediction works well, but not for forward branch

Approach: Branch prediction depends on history

#### Based on correlations

- Temporal correlation

If a branch was taken recently, it will probably be taken again (loops, etc.)

- Spatial correlation

Branches on an execution path will probably behave similarly with each execution of the path

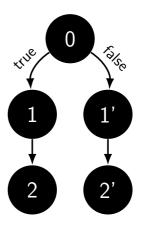

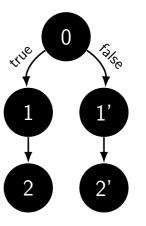

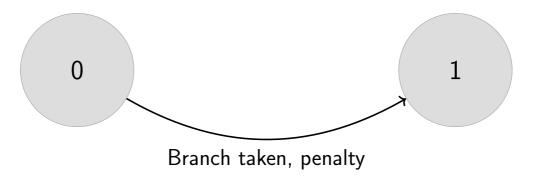

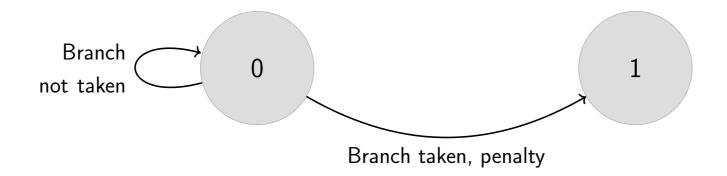

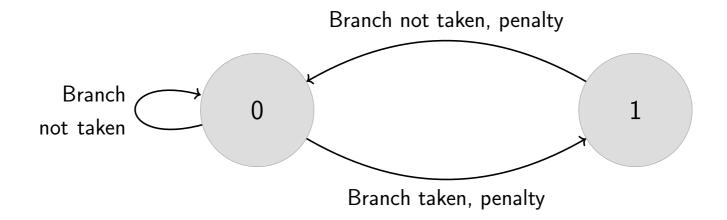

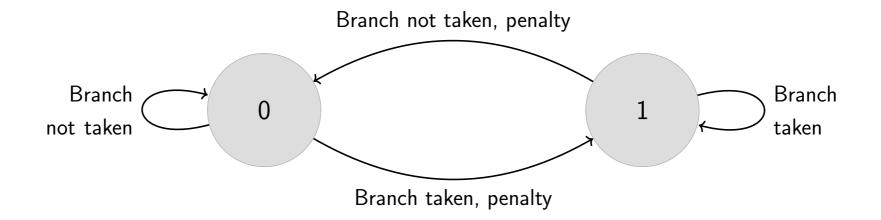

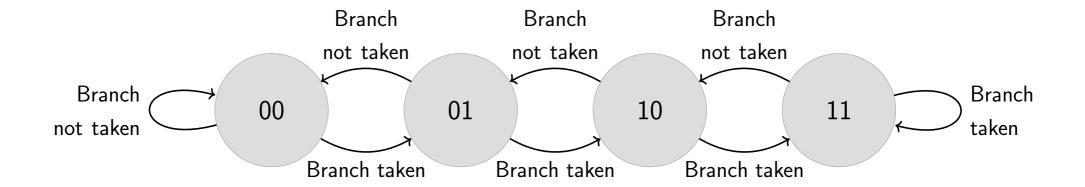

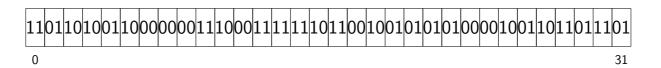

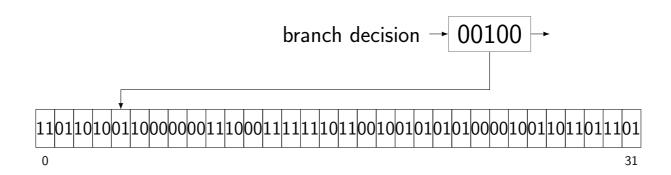

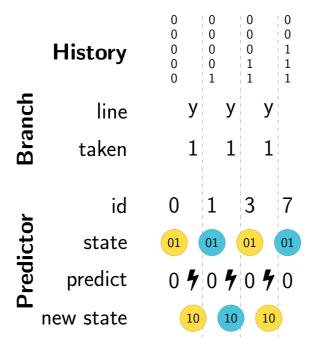

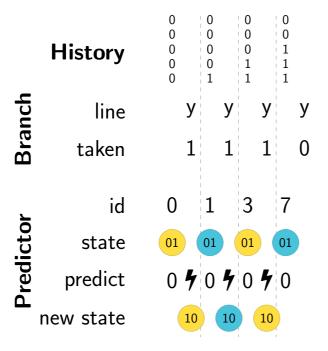

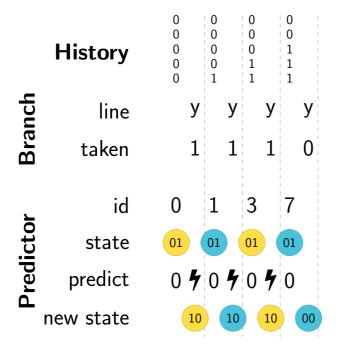

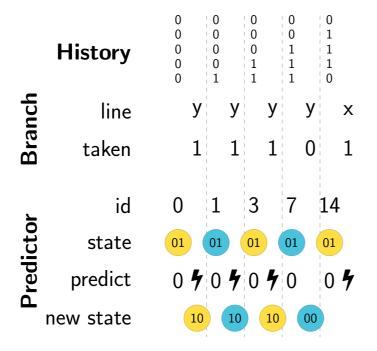

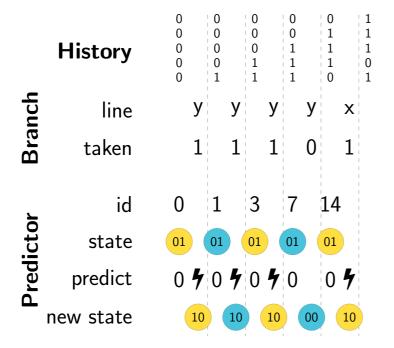

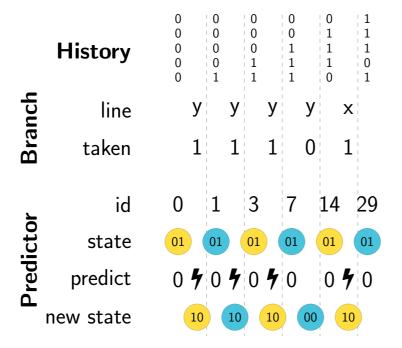

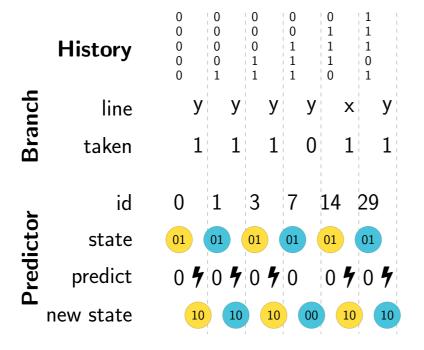

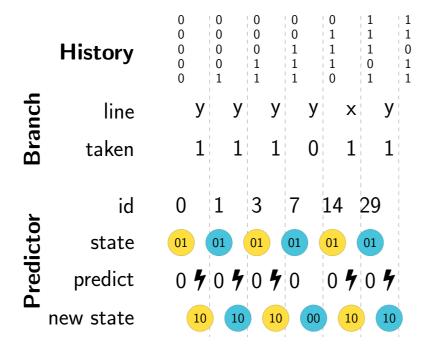

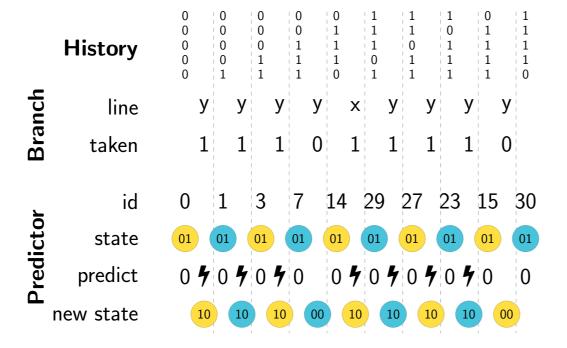

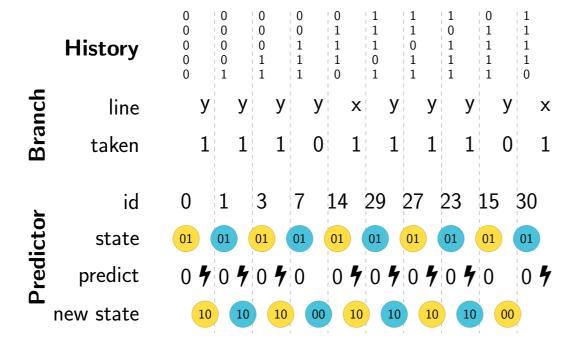

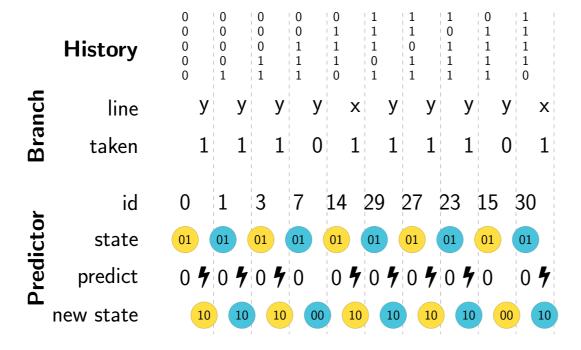

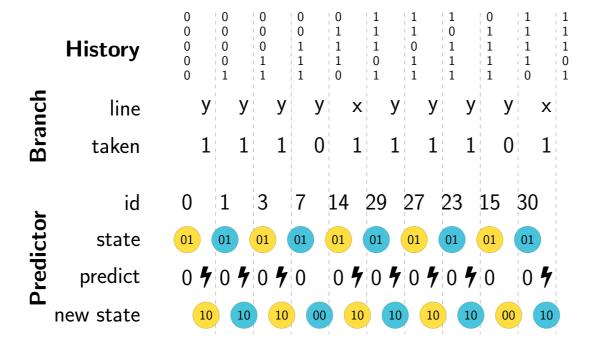

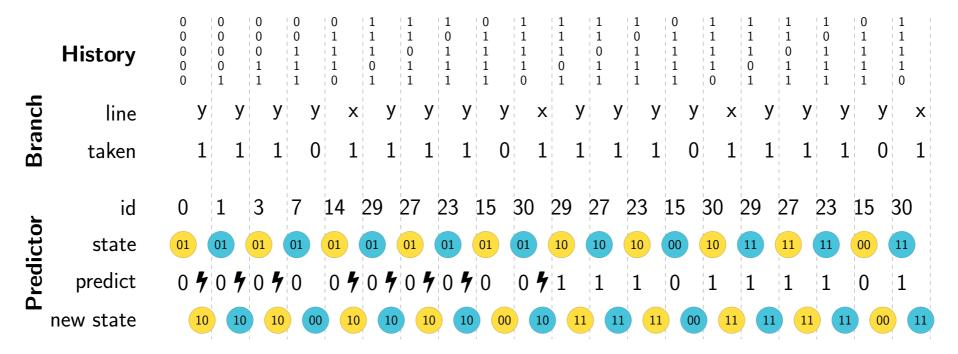

Idea: Consider last branch decision

0

Idea: Consider last branch decision

1 bit counter/state machine

0

1

Idea: Consider last branch decision

Idea: Consider last branch decision

Idea: Consider last branch decision

Idea: Consider last branch decision

|  |  |  |  | Predictor |

|--|--|--|--|-----------|

|  |  |  |  | 0         |

|  |  |  |  |           |

|  |  |  |  |           |

|  |  |  |  |           |

|  |  |  |  |           |

|  |  |  |  |           |

|  |  |  |  |           |

|  |  |  |  |           |

|  |  |  |  |           |

|  |  |  |  |           |

|   |   |   |   |   |   | Predict | OI |

|---|---|---|---|---|---|---------|----|

| 1 | 1 | 1 | 1 | 1 | 1 |         |    |

| beqz x10, 24 |  |  | 0 |

|--------------|--|--|---|

|              |  |  |   |

|              |  |  |   |

|              |  |  |   |

|              |  |  |   |

|              |  |  |   |

|              |  |  |   |

|              |  |  |   |

| PC      |              |  |  |  | Predictor |

|---------|--------------|--|--|--|-----------|

| [0×120] | beqz x10, 24 |  |  |  | 0         |

|         |              |  |  |  |           |

|         |              |  |  |  |           |

|         |              |  |  |  |           |

|         |              |  |  |  |           |

|         |              |  |  |  |           |

|         |              |  |  |  |           |

|         |              |  |  |  |           |

|         |              |  |  |  |           |

|         |              |  |  |  |           |

|         |              |  |  |  |           |

| PC      |              |    |  |  |  | Predictor |

|---------|--------------|----|--|--|--|-----------|

| [0×120] | beqz x10, 24 | FE |  |  |  | 0         |

|         |              |    |  |  |  |           |

|         |              |    |  |  |  |           |

|         |              |    |  |  |  |           |

|         |              |    |  |  |  |           |

|         |              |    |  |  |  |           |

|         |              |    |  |  |  |           |

|         |              |    |  |  |  |           |

|         |              |    |  |  |  |           |

|         |              |    |  |  |  |           |

|         |              |    |  |  |  |           |

| PC      |                         |    |  |  |  | Predictor |

|---------|-------------------------|----|--|--|--|-----------|

| [0×120] | beqz x10, 24            | FE |  |  |  | 0         |

| [0x124] | <b>slli</b> x11, x10, 2 |    |  |  |  | 0         |

|         |                         |    |  |  |  |           |

|         |                         |    |  |  |  |           |

|         |                         |    |  |  |  |           |

|         |                         |    |  |  |  |           |

|         |                         |    |  |  |  |           |

|         |                         |    |  |  |  |           |

|         |                         |    |  |  |  |           |

| PC      |                         |    |    |  |  |  | Predictor |

|---------|-------------------------|----|----|--|--|--|-----------|

| [0×120] | beqz x10, 24            | FE | DE |  |  |  | 0         |

| [0x124] | <b>slli</b> x11, x10, 2 |    | FE |  |  |  | 0         |

|         |                         |    |    |  |  |  |           |

|         |                         |    |    |  |  |  |           |

|         |                         |    |    |  |  |  |           |

|         |                         |    |    |  |  |  |           |

|         |                         |    |    |  |  |  |           |

|         |                         |    |    |  |  |  |           |

|         |                         |    |    |  |  |  |           |

| PC      |                         |    |    |    |  |  | Predictor |

|---------|-------------------------|----|----|----|--|--|-----------|

| [0×120] | beqz x10, 24            | FE | DE | EX |  |  | 0         |

| [0×124] | <b>slli</b> x11, x10, 2 |    | FE | DE |  |  | 0         |

| [0x128] | add x11, x11, x8        |    |    | FE |  |  | 0         |

|         |                         |    |    |    |  |  |           |

|         |                         |    |    |    |  |  |           |

|         |                         |    |    |    |  |  |           |

|         |                         |    |    |    |  |  |           |

|         |                         |    |    |    |  |  |           |

|         |                         |    |    |    |  |  |           |

| PC      |                         |    |    |    |    |  | Predictor |

|---------|-------------------------|----|----|----|----|--|-----------|

| [0×120] | beqz x10, 24            | FE | DE | EX | MA |  | 0         |

| [0×124] | <b>slli</b> x11, x10, 2 |    | FE | DE | EX |  | 0         |

| [0×128] | add x11, x11, x8        |    |    | FE | DE |  | 0         |

| [0x12c] | lw x12, 0(x11)          |    |    |    | FE |  | 0         |

|         |                         |    |    |    |    |  |           |

|         |                         |    |    |    |    |  |           |

|         |                         |    |    |    |    |  |           |

|         |                         |    |    |    |    |  |           |

|         |                         |    |    |    |    |  |           |

| PC      |                         |    |    |    |    |    |    |    |    | Predictor |

|---------|-------------------------|----|----|----|----|----|----|----|----|-----------|

| [0x120] | beqz x10, 24            | FE | DE | EX | MA | WB |    |    |    | 0         |

| [0×124] | <b>slli</b> x11, x10, 2 |    | FE | DE | EX | MA | WB |    |    | 0         |

| [0x128] | add x11, x11, x8        |    |    | FE | DE | EX | MA | WB |    | 0         |

| [0x12c] | lw x12, 0(x11)          |    |    |    | FE | DE | EX | MA | WB | 0         |

|         |                         |    |    |    |    |    |    |    |    |           |

|         |                         |    |    |    |    |    |    |    |    |           |

|         |                         |    |    |    |    |    |    |    |    |           |

|         |                         |    |    |    |    |    |    |    |    |           |

|         |                         |    |    |    |    |    |    |    |    |           |

| PC      |                         |    |    |    |    |    |    |    |    | Predictor |

|---------|-------------------------|----|----|----|----|----|----|----|----|-----------|

| [0×120] | beqz x10, 24            | FE | DE | EX | MA | WB |    |    |    | 0         |

| [0x124] | <b>slli</b> x11, x10, 2 |    | FE | DE | EX | MA | WB |    |    | 0         |

| [0x128] | add x11, x11, x8        |    |    | FE | DE | EX | MA | WB |    | 0         |

| [0x12c] | lw x12, 0(x11)          |    |    |    | FE | DE | EX | MA | WB | 0         |

|         | •••                     |    |    |    |    |    |    |    |    |           |

|         |                         |    |    |    |    |    |    |    |    |           |

|         |                         |    |    |    |    |    |    |    |    |           |

|         |                         |    |    |    |    |    |    |    |    |           |

|         |                         |    |    |    |    |    |    |    |    |           |

| PC      |                  |    |    |    |    |    |    |    |    | Predictor |

|---------|------------------|----|----|----|----|----|----|----|----|-----------|

| [0×120] | beqz x10, 24     | FE | DE | EX | MA | WB |    |    |    | 0         |

| [0×124] | slli x11, x10, 2 |    | FE | DE | EX | MA | WB |    |    | 0         |

| [0×128] | add x11, x11, x8 |    |    | FE | DE | EX | MA | WB |    | 0         |

| [0x12c] | lw x12, 0(x11)   |    |    |    | FE | DE | EX | MA | WB | 0         |

|         | •••              |    |    |    |    |    |    |    |    |           |

| [0×120] | beqz x10, 24     | FE |    |    |    |    |    |    |    | 0         |

|         |                  |    |    |    |    |    |    |    |    |           |

|         |                  |    |    |    |    |    |    |    |    |           |

|         |                  |    |    |    |    |    |    |    |    |           |

| PC      |                         |    |    |    |    |    |    |    |    | Predictor |

|---------|-------------------------|----|----|----|----|----|----|----|----|-----------|

| [0×120] | beqz x10, 24            | FE | DE | EX | MA | WB |    |    |    | 0         |

| [0×124] | <b>slli</b> x11, x10, 2 |    | FE | DE | EX | MA | WB |    |    | 0         |

| [0×128] | add x11, x11, x8        |    |    | FE | DE | EX | MA | WB |    | 0         |

| [0x12c] | lw x12, 0(x11)          |    |    |    | FE | DE | EX | MA | WB | 0         |

|         | •••                     |    |    |    |    |    |    |    |    |           |

| [0×120] | beqz x10, 24            | FE | DE |    |    |    |    |    |    | 0         |

| [0×124] | slli x11, x10, 2        |    | FE |    |    |    |    |    |    | 0         |

|         |                         |    |    |    |    |    |    |    |    |           |

|         |                         |    |    |    |    |    |    |    |    |           |

| PC      |                         |    |    |    |    |    |    |    |    | Predictor |

|---------|-------------------------|----|----|----|----|----|----|----|----|-----------|

| [0×120] | beqz x10, 24            | FE | DE | EX | MA | WB |    |    |    | 0         |

| [0×124] | <b>slli</b> x11, x10, 2 |    | FE | DE | EX | MA | WB |    |    | 0         |

| [0×128] | add x11, x11, x8        |    |    | FE | DE | EX | MA | WB |    | 0         |

| [0x12c] | lw x12, 0(x11)          |    |    |    | FE | DE | EX | MA | WB | 0         |

|         | •••                     |    |    |    |    |    |    |    |    |           |

| [0×120] | beqz x10, 24            | FE | DE | EX |    |    |    |    |    | 0         |

| [0×124] | <b>slli</b> x11, x10, 2 |    | FE | DE |    |    |    |    |    | 0         |

| [0×128] | add x11, x11, x8        |    |    | FE |    |    |    |    |    | 0         |

|         |                         |    |    |    |    |    |    |    |    |           |

| PC      |                         |    |    |    |    |    |    |    |    | Predictor |

|---------|-------------------------|----|----|----|----|----|----|----|----|-----------|

| [0x120] | beqz x10, 24            | FE | DE | EX | MA | WB |    |    |    | 0         |

| [0x124] | slli x11, x10, 2        |    | FE | DE | EX | MA | WB |    |    | 0         |

| [0x128] | add x11, x11, x8        |    |    | FE | DE | EX | MA | WB |    | 0         |

| [0x12c] | lw x12, 0(x11)          |    |    |    | FE | DE | EX | MA | WB | 0         |

|         | •••                     |    |    |    |    |    |    |    |    |           |

| [0x120] | beqz x10, 24            | FE | DE | EX |    |    |    |    |    | 0         |

| [0x124] | <b>slli</b> x11, x10, 2 |    | FE | DE |    |    |    |    |    | 0         |

| [0x128] | add x11, x11, x8        |    |    | FE |    |    |    |    |    | 0         |

|         |                         |    |    |    |    |    |    |    |    | 1         |

| PC      |                         |    |    |    |    |    |    |    |    | Predictor |

|---------|-------------------------|----|----|----|----|----|----|----|----|-----------|

| [0x120] | beqz x10, 24            | FE | DE | EX | MA | WB |    |    |    | 0         |

| [0x124] | <b>slli</b> x11, x10, 2 |    | FE | DE | EX | MA | WB |    |    | 0         |

| [0x128] | add x11, x11, x8        |    |    | FE | DE | EX | MA | WB |    | 0         |

| [0x12c] | lw x12, 0(x11)          |    |    |    | FE | DE | EX | MA | WB | 0         |

|         | •••                     |    |    |    |    |    |    |    |    |           |

| [0x120] | beqz x10, 24            | FE | DE | EX | MA |    |    |    |    | 0         |

| [0×124] | slli x11, x10, 2        |    | FE | DE |    |    |    |    |    | 0         |

| [0x128] | add x11, x11, x8        |    |    | FE |    |    |    |    |    | 0         |

| [0×148] | sll x9, x7, x10         |    |    |    | FE |    |    |    |    | 1         |

| PC      |                         |    |    |    |    |    |    |    |    | Predictor |

|---------|-------------------------|----|----|----|----|----|----|----|----|-----------|

| [0x120] | beqz x10, 24            | FE | DE | EX | MA | WB |    |    |    | 0         |

| [0x124] | <b>slli</b> x11, x10, 2 |    | FE | DE | EX | MA | WB |    |    | 0         |

| [0x128] | add x11, x11, x8        |    |    | FE | DE | EX | MA | WB |    | 0         |

| [0x12c] | lw x12, 0(x11)          |    |    |    | FE | DE | EX | MA | WB | 0         |

|         | •••                     |    |    |    |    |    |    |    |    |           |

| [0x120] | beqz x10, 24            | FE | DE | EX | MA | WB |    |    |    | 0         |

| [0x124] | slli x11, x10, 2        |    | FE | DE |    |    |    |    |    | 0         |

| [0x128] | add x11, x11, x8        |    |    | FE |    |    |    |    |    | 0         |

| [0x148] | sll x9, x7, x10         |    |    |    | FE | DE | EX | MA | WB | 1         |

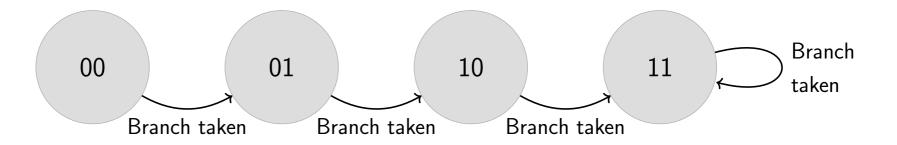

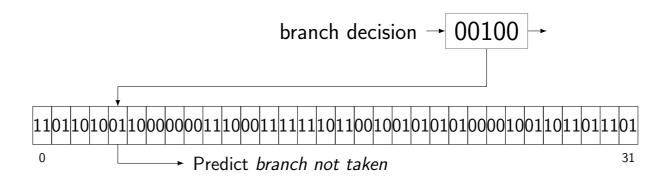

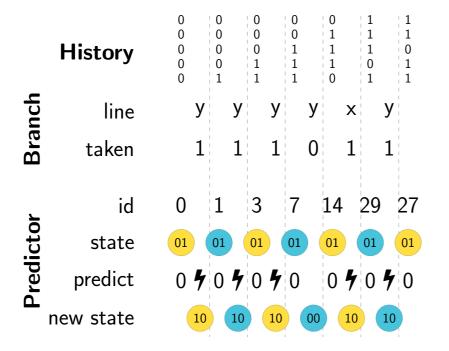

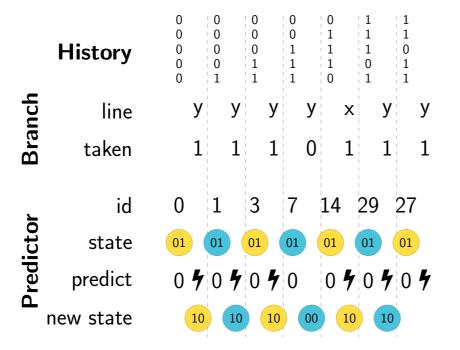

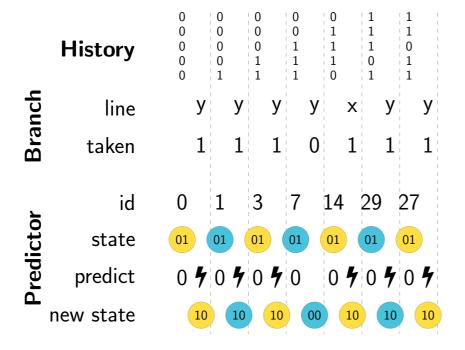

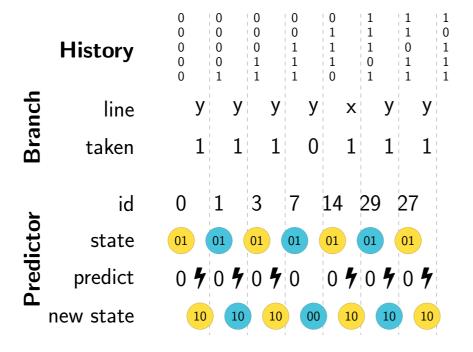

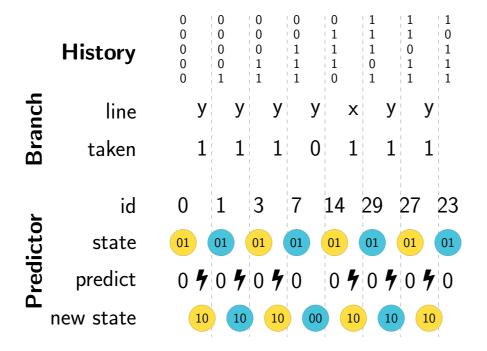

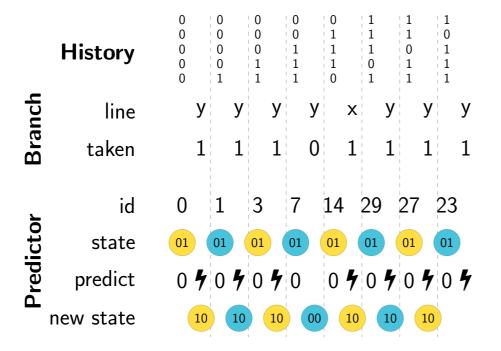

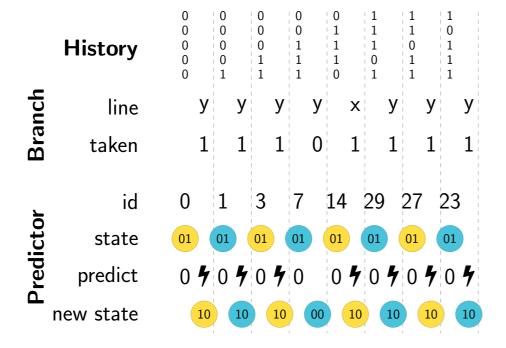

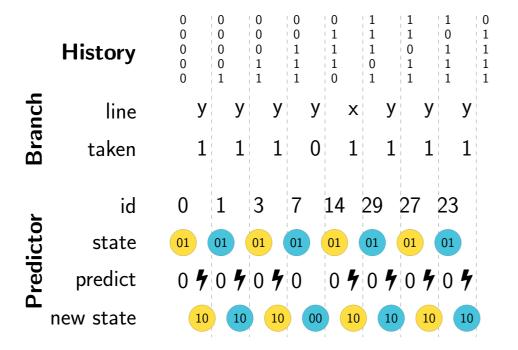

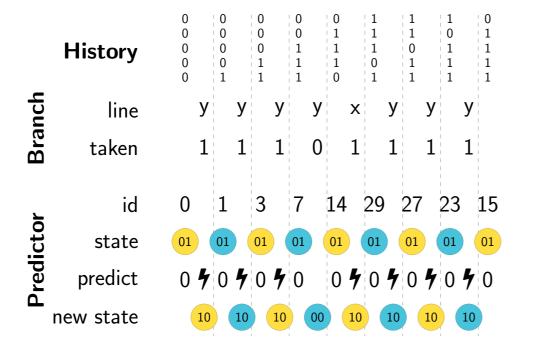

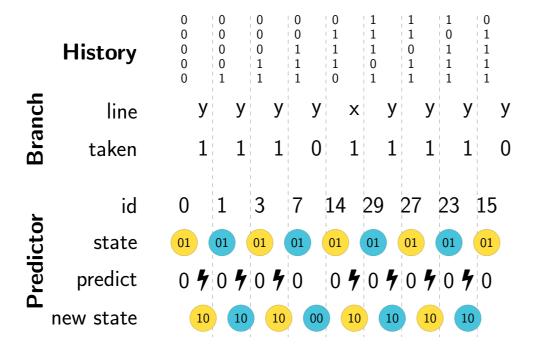

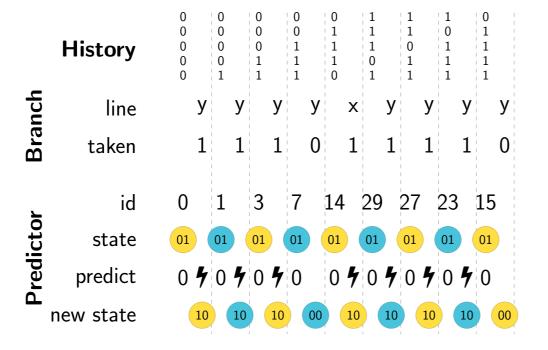

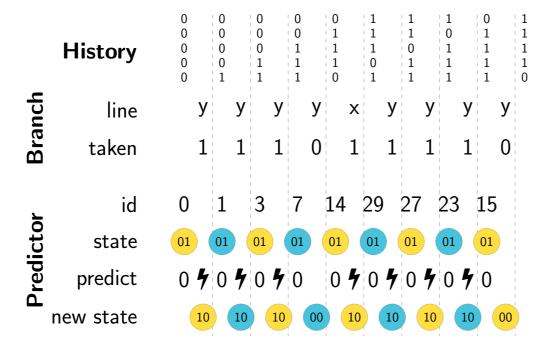

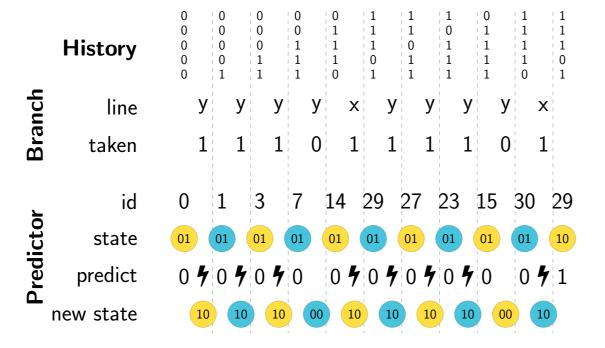

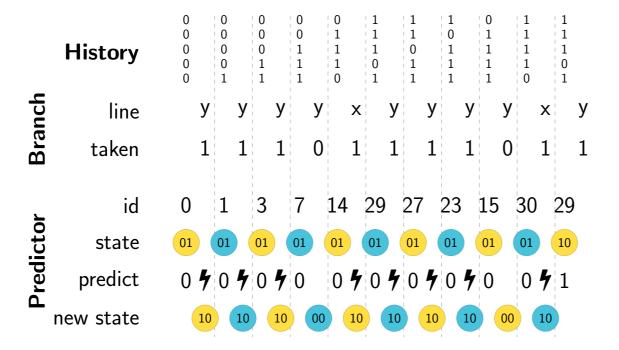

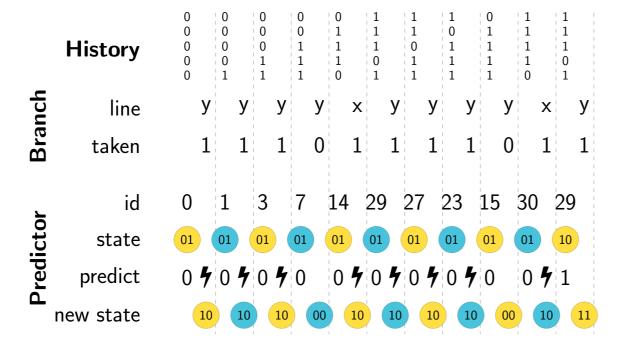

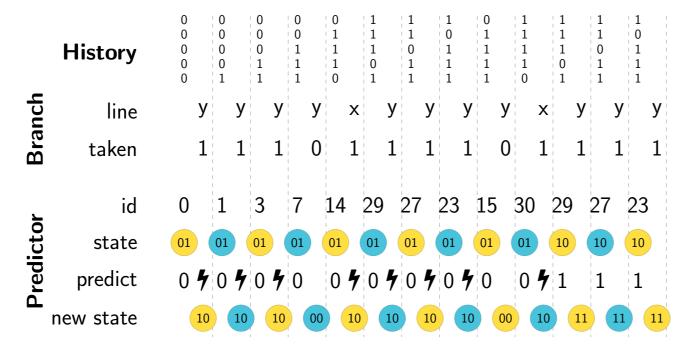

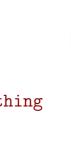

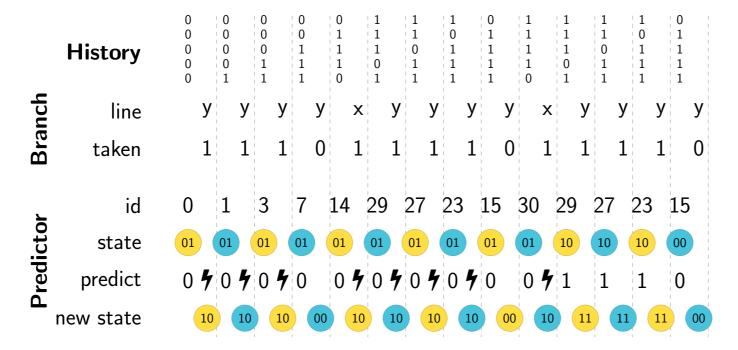

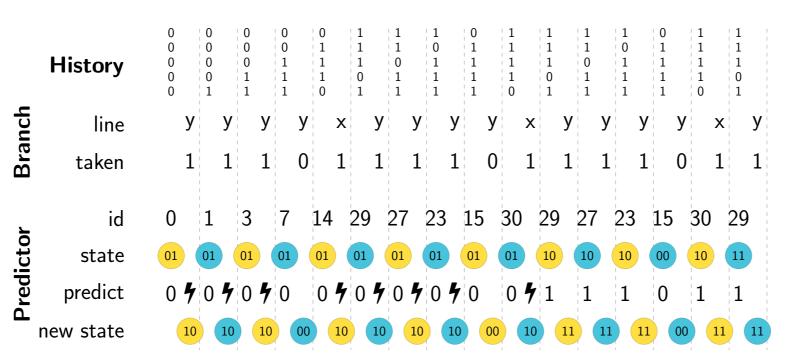

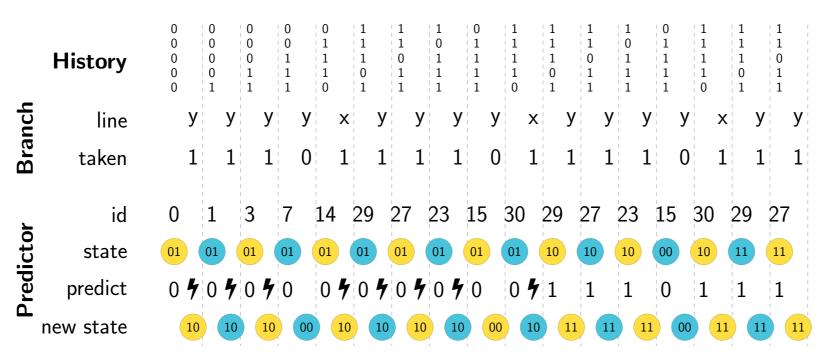

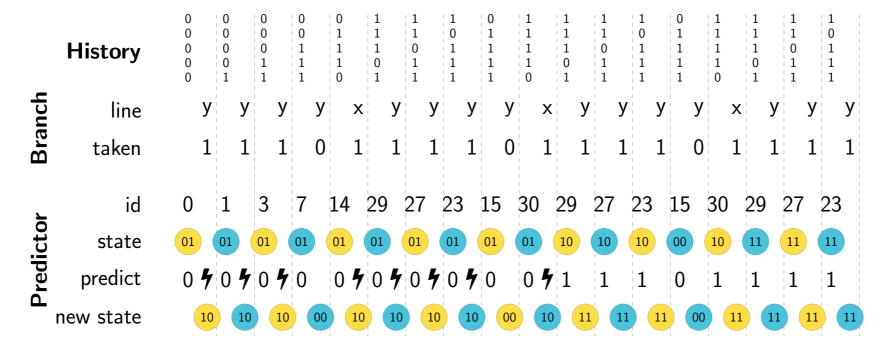

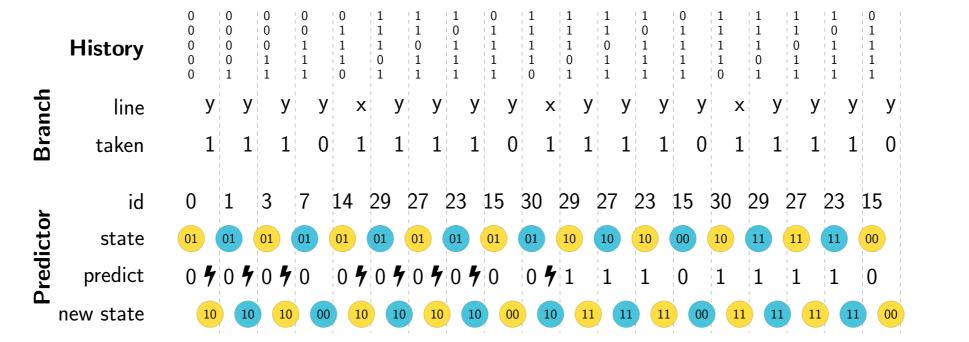

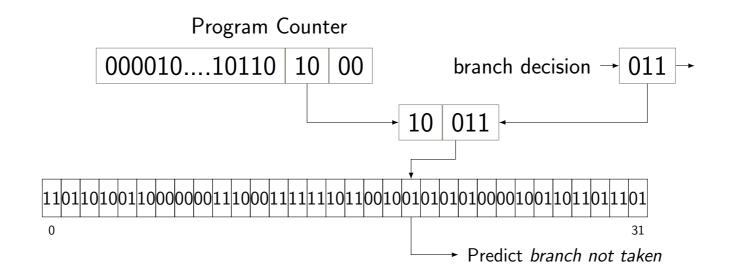

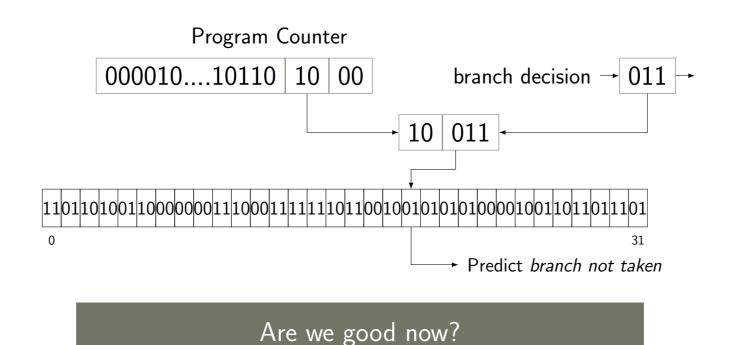

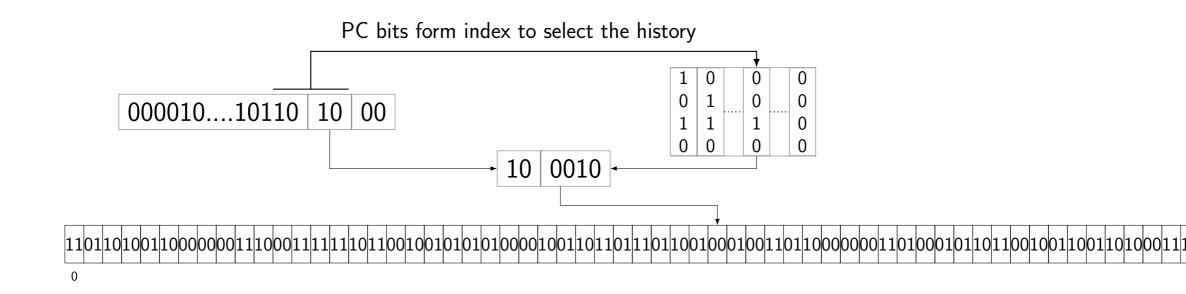

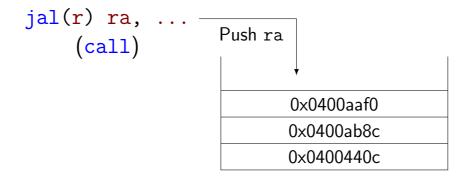

Single bit to track all branches

Single bit to track all branches

Problem: Multiple branches

Single bit to track all branches

Problem: Multiple branches

Nested loop, control structures, function calls

Single bit to track all branches

Problem: Multiple branches